# Block Arithmetic Techniques for the Implementation of Deep Neural Networks

# WENJIE ZHOU

Supervisor: Philip H.W. Leong Associate Supervisor: David Boland

A thesis submitted in fulfilment of the requirements for the degree of Doctor of Philosophy

School of Electrical and Computer Engineering

Faculty of Engineering

The University of Sydney

Australia

14 December 2025

#### **Abstract**

The success of artificial intelligence (AI) models, especially deep neural network (DNN)s, has attracted tremendous investment in developing the latest AI models by private and government departments. Performance is crucial for the evolution of DNNs, particularly as computational requirements are surging. Along with increasing DNN model scale, the training cost is becoming a new problem for DNNs.

One of the critical techniques for energy-efficient training is low-precision arithmetic. Block arithmetic is a promising technique that reduces precision requirements and power consumption. This method further reduces the word length of the element, and the shared exponent expands their dynamic range.

This thesis aims to develop an improved block arithmetic algorithm and implementation methodology. At the arithmetic level, this work investigates the implementation of block arithmetic. At the general matrix multiplication (GEMM) kernel level, this dissertation examines kernel design under different block arithmetic implementations. For rescaling, this work further addresses the challenges associated with block arithmetic and introduces the proposed delayed scaling method called the delay update. At the application level, this work utilizes neural basis expansion analysis for interpretable time series analysis (N-BEATS) based inference and training accelerators to demonstrate the advantages of block arithmetic.

The contributions of this work are as follows: Firstly, we propose the block minifloat (BM) implementation for inference, the first implementation of an field programmable gate array (FPGA) based accelerator using BM arithmetic during publication, demonstrating hardware efficiency and accuracy benefits over integer and floating point on N-BEATS. Secondly, we propose the BM implementation for training, in the form of the first FPGA implementation of a 4-bit BM, mixed-precision neural network training of N-BEATS. Thirdly, we propose the delay update method to reduce the rescaling computation in block arithmetic. Empirical

iv ABSTRACT

studies show that the delay update scheme achieves nearly the same accuracy as the commonly used maximum calibration method, with a significant hardware implementation advantage.

In summary, this dissertation shows how block arithmetic can benefit neural network inference and training. These research outcomes demonstrate that block arithmetic can offer the same accuracy as the contemporary approaches using integer and floating point, with lower precision leading to lower resource utilization.

### Acknowledgements

I'm grateful to have finally completed the long and arduous journey of my PhD. The challenges I faced were not only academic, but also many circumstances beyond my control. The COVID-19 pandemic disrupted both research and daily life, while the rising cost of living added further difficulties. Overcoming these problems has made this accomplishment even more meaningful.

I want to express my gratitude to my supervisor, Philip Leong. In daily life, he always cares for his students and provides support. In research, he not only provided detailed, insightful academic feedback but also offered a visionary perspective that elevated the quality of my research. We often held different views but always agreed on one principle: pursuing practical, high-quality research.

I would also like to express my thanks to my father. He provided financial and emotional support throughout my doctoral studies. During these years, he also took on the responsibility of caring for my grandparents and managing the family finances, which allowed me to focus on my research without distraction.

Additionally, I would like to express my sincere gratitude to everyone who supported me throughout my PhD journey. Their encouragement and assistance have been invaluable in helping me reach this stage. Finally, this research reported in this thesis was supported by the award of a University of Sydney International Student (USYDIS) scholarship to the PhD Candidate.

### **Authorship Attribution Statement**

This thesis includes material that has been previously published or prepared for publication during my PhD studies under the supervision of Professor Philip H.W. Leong. The ideas and development of each publication are primarily my own work, carried out under the guidance of my supervisors and with the assistance acknowledged below:

- Professor Philip H.W. Leong provided overall research direction and guidance throughout my PhD.

- Chapter 3: Professor Leong proposed the concept of implementing N-BEATS inference using BM. I developed the BM-based N-BEATS inference accelerator and introduced the integer-based block arithmetic implementation. Professor Leong and David Boland contributed to idea refinement, provided implementation guidance, and assisted in polishing the manuscript. Haoyan Qi supported the implementation of the host control system.

- Chapter 4: Professor Leong suggested the implementation of N-BEATS neural network training using BM. I designed the BM-based N-BEATS training accelerator and proposed the ideas. Professor Leong and David Boland helped refine the ideas, guided the implementation, and contributed to manuscript preparation. Haoyan Qi assisted with the host control system implementation.

- Chapter 5: Professor Leong introduced the concept of developing a delayed scaling algorithm. I proposed the delay update algorithm and conducted the GEMM kernel performance analysis. Professor Leong provided guidance and support throughout the development process.

### **Artificial Intelligence Statement**

During the preparation of the thesis, the author used M365 Copilot for the purposes of text enhancement (e.g., spelling, sentence structure, grammar). The author confirms that where text was modified by generative AI, the content was reviewed for possible errors, inaccuracies, and bias. The author takes full responsibility for the submitted thesis and ensures the work is their own and has used generative AI within the parameters of use (refer to the University of Sydney generative AI guide for researchers).

### **Contents**

| Abstract     |                                          | iii |

|--------------|------------------------------------------|-----|

| Acknowle     | dgements                                 | v   |

| Authorshi    | p Attribution Statement                  | vi  |

| Artificial 1 | Intelligence Statement                   | vii |

| Contents     |                                          | vii |

| List of Fig  | gures                                    | xi  |

| Chapter 1    | Introduction                             | 1   |

| 1.1 M        | otivation                                | 1   |

| 1.2 Ai       | ms and Contributions                     | 4   |

| 1.3 Th       | esis Structure                           | 6   |

| Chapter 2    | Background                               | 7   |

| 2.1 M        | achine Learning                          | 7   |

| 2.1.1        | Types of Machine Learning                | 8   |

| 2.1.2        | 2 Supervised Learning System             | 9   |

| 2.1.3        | B Deep Neural Network Training           | 12  |

| 2.2 Li       | terature overview                        | 18  |

| 2.2.         | Challenge in Training Acceleration       | 18  |

| 2.2.2        | Related Works                            | 20  |

| 2.3 Lo       | w-precision arithmetic used for training | 24  |

| 2.3.1        | Fixed Point                              | 24  |

| 2.3.2        | Ploating Point                           | 26  |

| 2.3.3        | Block Arithmetic                         | 29  |

| 2.4  | Sum            | mary                                           | 37 |

|------|----------------|------------------------------------------------|----|

| Chap | oter 3         | Block Minifloat Arithmetic for Inference       | 39 |

| 3.1  | Intro          | oduction                                       | 39 |

| 3.2  | BM             | arithmetic implementation                      | 40 |

|      | 3.2.1          | Inner Product                                  | 41 |

|      | 3.2.2          | Rescaling                                      | 42 |

|      | 3.2.3          | BM Vector Addition                             | 46 |

| 3.3  | N-B            | EATS Inference Implementation                  | 48 |

|      | 3.3.1          | BM Systolic Array                              | 48 |

|      | 3.3.2          | N-BEATS Inference Accelerator                  | 49 |

| 3.4  | Resu           | ılts                                           | 51 |

|      | 3.4.1          | Experimental Configuration                     | 51 |

|      | 3.4.2          | Accuracy and Performance                       | 53 |

| 3.5  | Sum            | mary                                           | 55 |

| Chap | oter 4         | Block Minifloat Artithmetic for Training       | 57 |

| 4.1  | Intro          | oduction                                       | 57 |

| 4.2  | Bacl           | kground                                        | 59 |

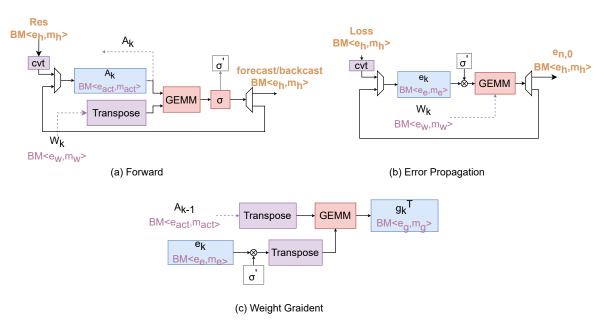

|      | 4.2.1          | Forward and Backward Pass for an N-BEATS Block | 59 |

|      | 4.2.2          | Stochastic Rounding                            | 63 |

|      | 4.2.3          | Related Work                                   | 63 |

| 4.3  | Imp            | lementation of BM Arithmetic                   | 65 |

|      | 4.3.1          | Cross-block BM Matrix Multiplication           | 65 |

|      | 4.3.2          | BM Vector Addition                             | 69 |

|      | 4.3.3          | BM GEMM Kernel Architecture                    | 71 |

|      | 4.3.4          | DSP Packing for 4-bit BM Training              | 73 |

| 4.4  | N-B            | EATS Training Accelerator                      | 76 |

|      |                | EATS Training Accelerator                      | 70 |

|      | 4.4.1          | Training Accelerator Design                    | 76 |

|      | 4.4.1<br>4.4.2 |                                                |    |

x Contents

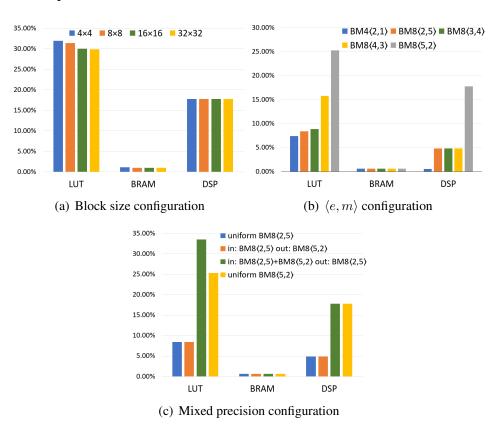

| 4.5.1       | Experimental Setting                           | 80  |

|-------------|------------------------------------------------|-----|

| 4.5.2       | BM GEMM Area Exploration                       | 82  |

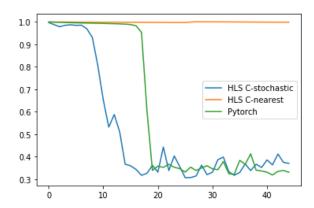

| 4.5.3       | Effect of Rounding Scheme                      | 83  |

| 4.5.4       | Accuracy and Performance of N-BEATS Training   | 83  |

| 4.6 Sum     | nmary                                          | 86  |

| Chapter 5   | Delay Update: efficient rescaling for training | 89  |

| 5.1 Intro   | oduction                                       | 89  |

| 5.2 Bac     | kground                                        | 92  |

| 5.2.1       | Rescaling Methods                              | 92  |

| 5.2.2       | Other Scaling Methods                          | 94  |

| 5.3 GEN     | MM Performance Analysis                        | 95  |

| 5.3.1       | $B \ge T$ Case                                 | 97  |

| 5.3.2       | T > B Case                                     | 99  |

| 5.4 Dela    | ay Update Algorithm                            | 104 |

| 5.5 Resi    | ults                                           | 107 |

| 5.6 Sum     | nmary                                          | 115 |

| Chapter 6   | Conclusion                                     | 117 |

| 6.1 Futu    | re Outlook                                     | 118 |

| 6.1.1       | Block Arithmetic                               | 118 |

| 6.1.2       | Hardware-efficient Training Algorithm          | 119 |

| Bibliograph | ny                                             | 121 |

# **List of Figures**

| 1.1 | Estimated training cost of select AI models, 2016-24 (Source: Epoch AI, 2024)                         |    |

|-----|-------------------------------------------------------------------------------------------------------|----|

|     | [111]                                                                                                 | 2  |

| 1.2 | The contribution and structure of the thesis.                                                         | 5  |

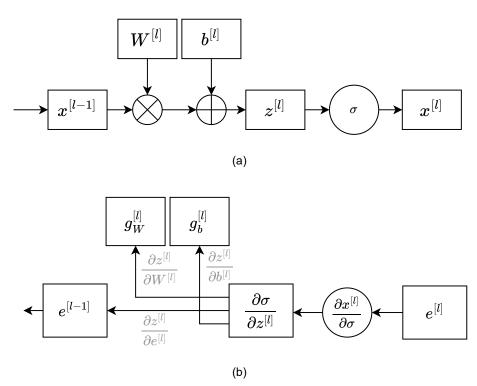

| 2.1 | Forward and backward pass of the $l$ -th fully connected (FC) layer in the multilayer                 |    |

|     | perceptron (MLP) example. The left block illustrates the forward pass, while                          |    |

|     | the three blocks on the right represent the backward pass. Solid lines indicate                       |    |

|     | computation flows, and dashed lines denote data read/write operations to memory.                      |    |

|     | Blue blocks represent data that must be stored in memory during forward and                           |    |

|     | backpropagation. Computation blocks are highlighted with semi-transparent red                         |    |

|     | overlays.                                                                                             | 14 |

| 2.2 | a multilayer perceptron (MLP) network example. (a) is a $n$ input neuron. (b) is a                    |    |

|     | three-layer multilayer perceptron (MLP) network.                                                      | 15 |

| 2.3 | The forward and backward pass of a fully connected (FC) layer. (a) is the forward                     |    |

|     | pass (inference), (b) is the backward pass.                                                           | 18 |

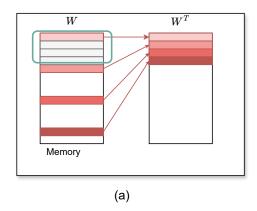

| 2.4 | Techniques for addressing the transposition problem. (a) Data rearrangement. (b)                      |    |

|     | Data path configuration. The uncolored/colored bars in the memory block represent                     |    |

|     | elements of $W$ , with word lengths depending on specific applications (e.g., 8-bit or                |    |

|     | 16-bit).                                                                                              | 21 |

| 2.5 | Illustration of direct feedback alignment.                                                            | 22 |

| 2.6 | Unsigned fixed-point arithmetic scheme.                                                               | 25 |

| 2.7 | floating-point (FP) arithmetic structure                                                              | 26 |

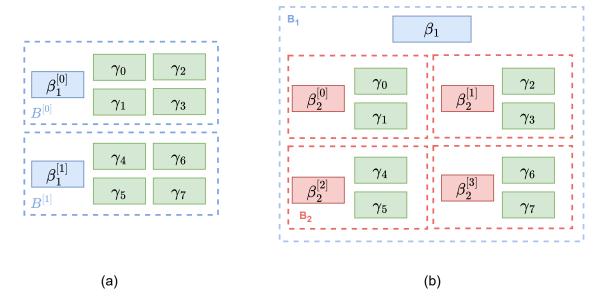

| 2.8 | An illustrative example of block arithmetic. (a) Block arithmetic with one-level                      |    |

|     | shared exponent. The block size in this example is 4. (b) Block arithmetic with                       |    |

|     | two-level shared exponents $\beta_1$ and $\beta_2$ . In this example, the first-level block $B_1$ has |    |

|     | a block size of 4, and the second-level block $B_2$ has a block size of 2.                            | 29 |

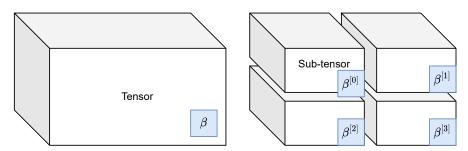

| 2.9  | An example of a global block and a local block. The tensor in the example is a                        |    |

|------|-------------------------------------------------------------------------------------------------------|----|

|      | three-dimensional tensor. (a) Global block example. (b) Local block example.                          | 30 |

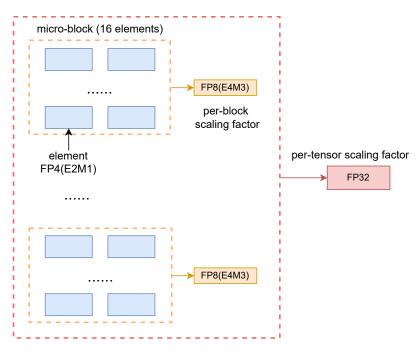

| 2.10 | The structure of NVFP4 arithmetic.                                                                    | 36 |

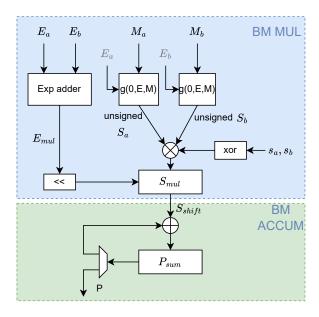

| 3.1  | The BM multiply accumulate (MAC) unit design for the global block.                                    | 42 |

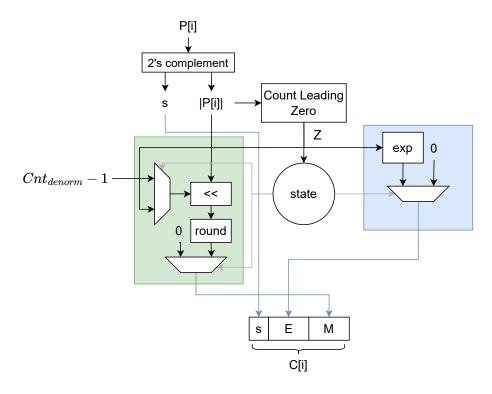

| 3.2  | The normalization implementation in $KulToBM$ . The left green block is                               |    |

|      | responsible for mantissa computation, and the right blue block is responsible for                     |    |

|      | exponent computation.                                                                                 | 44 |

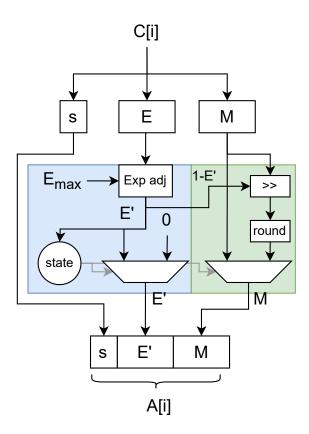

| 3.3  | Exponent Alignment computation implementation in $ExpAlign$ function. The left                        |    |

|      | blue block is responsible for the exponent computation, and the right green block is                  |    |

|      | responsible for the mantissa computation.                                                             | 46 |

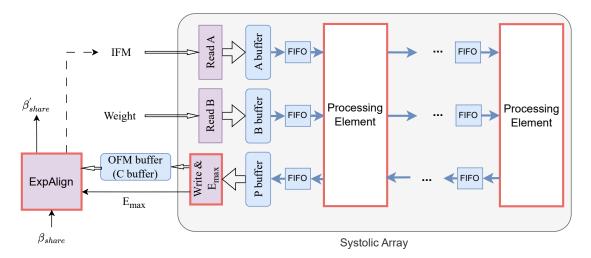

| 3.4  | The BM systolic array implementation. The red block represents the BM related                         |    |

|      | computation.                                                                                          | 48 |

| 3.5  | processing element (PE) design of the BM systolic array. Red blocks represent the                     |    |

|      | BM related computation.                                                                               | 49 |

| 3.6  | N-BEATS neural network model.                                                                         | 50 |

| 3.7  | N-BEATS Inference Accelerator.                                                                        | 51 |

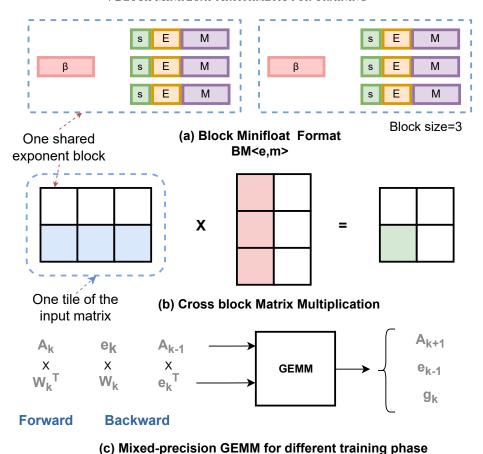

| 4.1  | Summary of the main ideas introduced in this paper. (a) BM format with block size                     |    |

|      | 3. (b) cross-block matrix multiplication. The shaded parts show a single block                        |    |

|      | output obtained by multiplying $1\times 3$ blocks by $3\times 1$ blocks. (c) GEMM kernel.             |    |

|      | Forward and backward passes are processed by the same GEMM accelerator at                             |    |

|      | different precisions.                                                                                 | 58 |

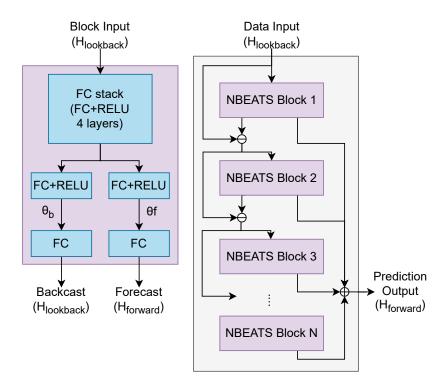

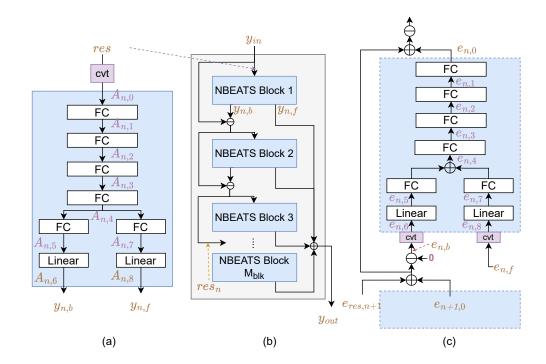

| 4.2  | N-BEATS neural network model. Variables in yellow represent high-precision                            |    |

|      | BM data (BM $\langle e_h, m_h \rangle$ ). $Cvt$ block is the precision conversion block that converts |    |

|      | high-precision data to low-precision data. (a) shows the N-BEATS block. The                           |    |

|      | input of each block is first converted to low-precision format, then goes first to                    |    |

|      | the 4-layer fully connected (FC) stack, and then the fully connected (FC) stack                       |    |

|      | output activation goes to the backcast branch and forecast branch. (b) shows the                      |    |

|      | N-BEATS model. (c) shows the error propagation of N-BEATS block.                                      | 60 |

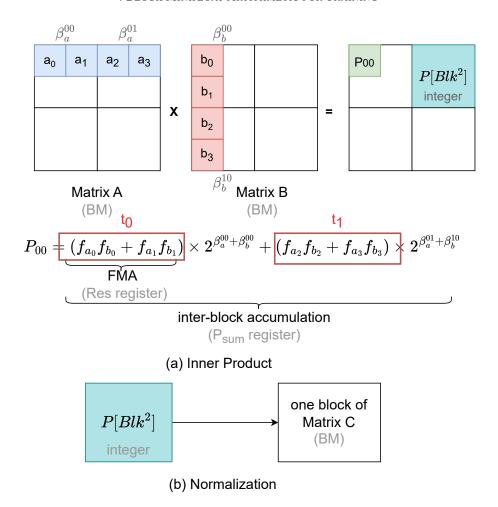

| 4.3  | Simplified example of a BM GEMM requiring inner-product and post-inner-product                        |    |

|      | (rescaling) computations. The matrices are $4 \times 4$ and each divided into $4, 2 \times 2$         |    |

LIST OF FIGURES xiii

|      | blocks. (a) Illustrates the fused multiply accumulate (FMA), the inputs are                                 |    |

|------|-------------------------------------------------------------------------------------------------------------|----|

|      | converted to integer, multiplied and added together to form $t_0=f_{a_0}f_{b_0}+f_{a_1}f_{b_1}$ and         |    |

|      | $t_1=f_{a_2}f_{b_2}+f_{a_3}f_{b_3}.$ In the inter-block accumulation step, the $t_i$ values are aligned     |    |

|      | according to the shared exponent values and summed to give a high-precision                                 |    |

|      | inner-product $P_{00}$ . The $P_{ij}$ values for a block are saved in a wide integer buffer                 |    |

|      | called $P[B_k^2]$ . (b) The rescaling process is executed after all the inner products                      |    |

|      | required for a particular block have been completed. The wide integer results are                           |    |

|      | converted into BM format data and form part of the output matrix C.                                         | 66 |

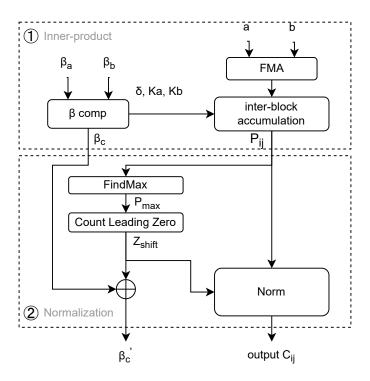

| 4.4  | Block diagram illustrating cross-block BM matrix multiplication. The first step                             |    |

|      | performs the minifloat fused multiply accumulate (FMA) (FMA block) and shared                               |    |

|      | exponent computation ( $\beta$ comp block), placing the result in $P[B_k^2]$ . In the second                |    |

|      | step, each $P_{ij}$ in $P[B_k^2]$ is examined to determine the appropriate shift for rescaling,             |    |

|      | which is performed in the Norm block. The resulting C output is in BM format.                               | 67 |

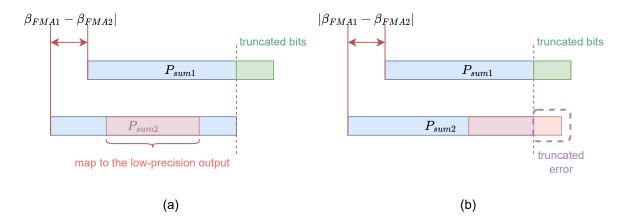

| 4.5  | The truncation error in aligned addition computation.                                                       | 68 |

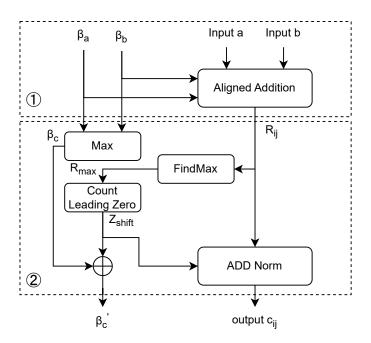

| 4.6  | BM vector addition arithmetic. The first step converts the inputs a and b into                              |    |

|      | integers, aligns them, and sums. The output $R_{ij}$ is placed in the signed integer                        |    |

|      | block $R[B_k^2]$ . The second step computes the output shared exponent $\beta_c$ . If there is              |    |

|      | overflow, it calculates the $Z_{\mathrm{shift}}$ value and adjusts $\beta_c$ , then the norm block converts |    |

|      | integer values in $R[B_k^2]$ into BM format.                                                                | 70 |

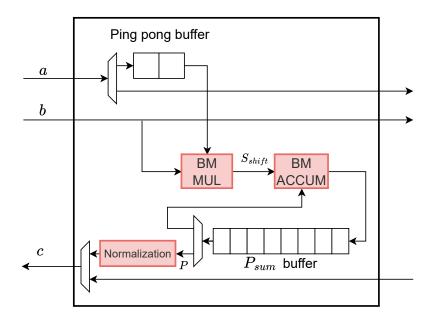

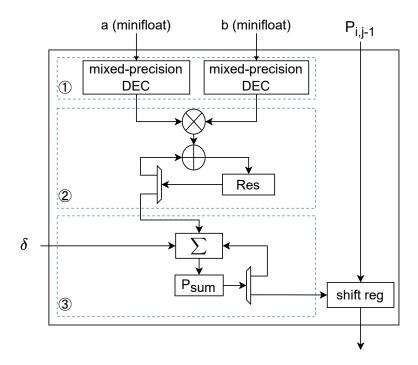

| 4.7  | processing element (PE) design of GEMM kernel. The processing element (PE) is                               |    |

|      | responsible for the scalar inner-product computation in Figure 4.3.                                         | 71 |

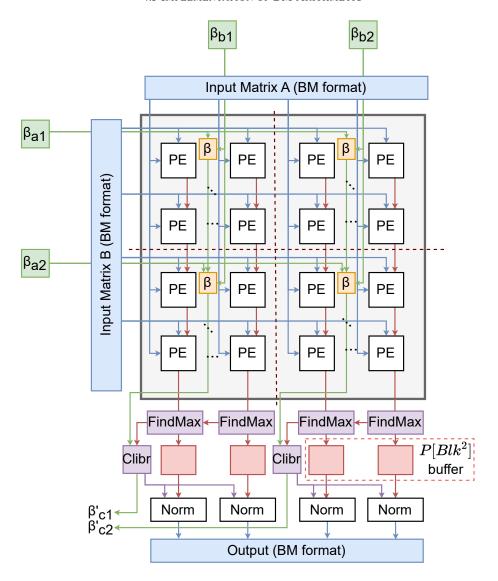

| 4.8  | Block size configurable GEMM kernel with tile size $T \times T$ ( $T=4$ ). The red                          |    |

|      | dashed lines represent the boundaries of the block, and the block size in this                              |    |

|      | example is $\frac{T}{2} \times \frac{T}{2}$ . The GEMM kernel is the implementation of Figure 4.4           | 73 |

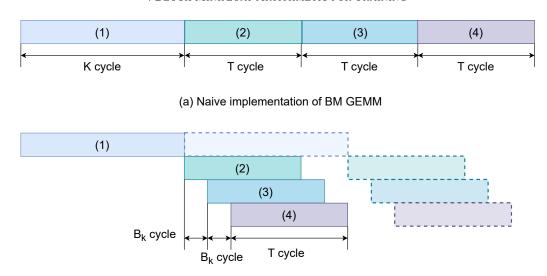

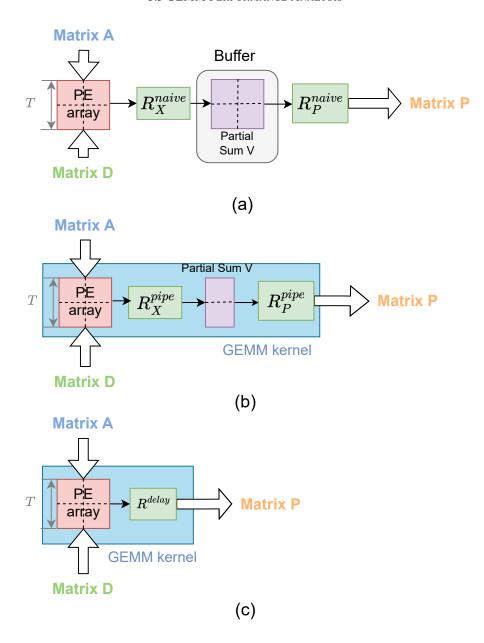

| 4.9  | Pipeline organization for BM GEMM. (a) is a naive implementation, (b) is the                                |    |

|      | fine-grained pipeline for BM GEMM. (1) is inner product; (2) is Find Max in each                            |    |

|      | column, and stream $P_{sum}$ to $P[B_k^2]$ buffer; (3) is Find Max $P_{max}$ in each block by               |    |

|      | left shifting, and calculate $Z_{\text{shift}}$ , $\beta_c'$ in Clibr block; (4) is Norm.                   | 74 |

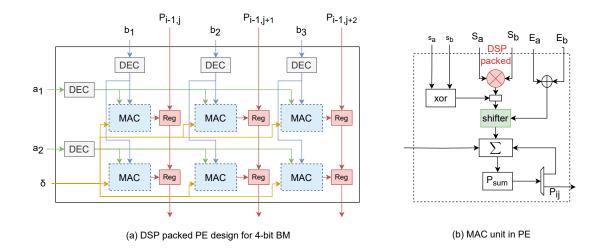

| 4.10 | DSP packed processing element (PE) design for 4-bit BM multiply accumulate                                  |    |

(MAC). (a) is the processing element (PE) design, the DEC block is the mixed

|      | precision decoder, and the Reg block is the shift register to pipeline out the           |    |

|------|------------------------------------------------------------------------------------------|----|

|      | accumulation result $P_{ij}$ . (b) is the multiply accumulate (MAC) unit design.         | 75 |

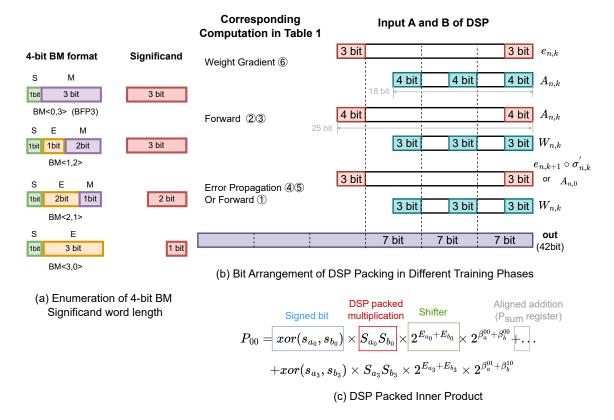

| 4.11 | DSP packing scheme for mixed precision 4-bit BM multiply accumulate (MAC).               |    |

|      | (a) is the bit arrangement for DSP packing in different training phases. The total       |    |

|      | number of multiplications is six, with two numbers in input A, three numbers             |    |

|      | in input B, and six 7-bit numbers in output C. (b) is the simplified example of          |    |

|      | DSP-packed inner product implementation. Based on Figure 4.3, the inner product          |    |

|      | merges the fused multiply accumulate (FMA) and inter-block accumulation as one           |    |

|      | step.                                                                                    | 76 |

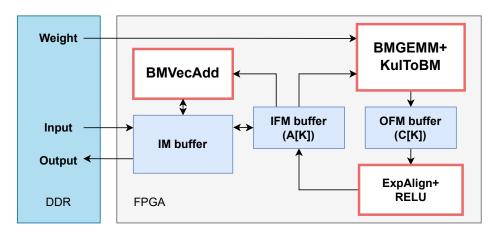

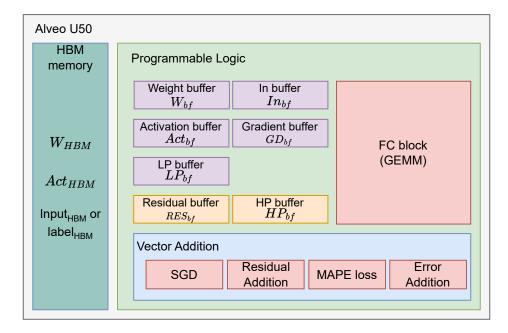

| 4.12 | N-BEATS training accelerator. The computing block is marked with red; the                |    |

|      | low-precision BM buffer is marked purple; the high-precision BM buffer is marked         |    |

|      | yellow. Fully connected (FC) block is illustrated in Figure 4.13                         | 77 |

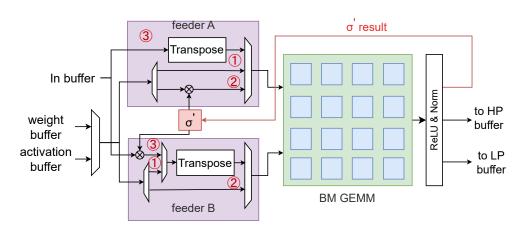

| 4.13 | fully connected (FC) block diagram. FeederA and FeederB have multiple paths for          |    |

|      | different training phases. (1) is the forward propagation; (2) is error propagation; (3) |    |

|      | is gradient computation. The BM GEMM is illustrated in Figure 5.2, but the Norm          |    |

|      | block in the GEMM is changed to rectified linear unit (ReLu)&Norm block.                 | 79 |

| 4.14 | Illustration of the forward and backward computation steps of an fully connected         |    |

|      | (FC) block. The dashed line represents the data that needs to be read/written            |    |

|      | between the HBM memory and the on-chip buffer. The blue box represents the               |    |

|      | data stored in the on-chip buffer; the red box represents the computing blocks.          | 81 |

| 4.15 | BM GEMM area comparison under different configuration                                    | 82 |

| 4.16 | Effect of different rounding schemes with tiny N-BEATS training example                  | 84 |

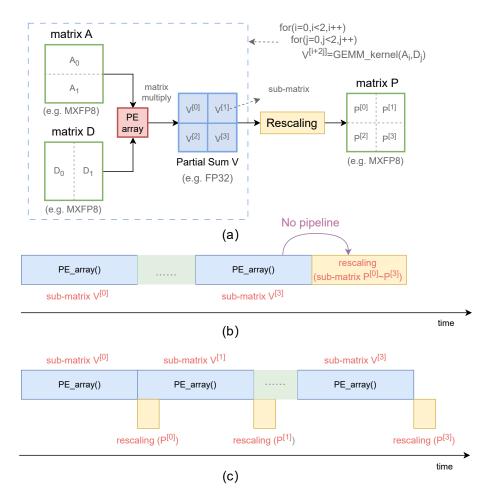

| 5.1  | Rescaling computation. (a) Example of rescaling in microscaling (MX)-format              |    |

|      | GEMM computation. Matrices A, D, and P represent the low-precision input and             |    |

|      | output matrices with global blocks, while matrix V denotes the high-precision            |    |

|      | partial sum matrix. Rescaling converts the high-precision partial sum into the           |    |

|      | low-precision output. (b) Example of GEMM using the maximum calibration                  |    |

|      | method. In this approach, rescaling can only begin after the matrix multiplication       |    |

|      | of all submatrices is completed. (c) Example of GEMM using the delayed scaling           |    |

|      |                                                                                          |    |

LIST OF FIGURES xv

|      | method. Each submatrix can be rescaled immediately after its multiplication              |     |

|------|------------------------------------------------------------------------------------------|-----|

|      | finishes, allowing matrix multiplication to be pipelined with rescaling.                 | 91  |

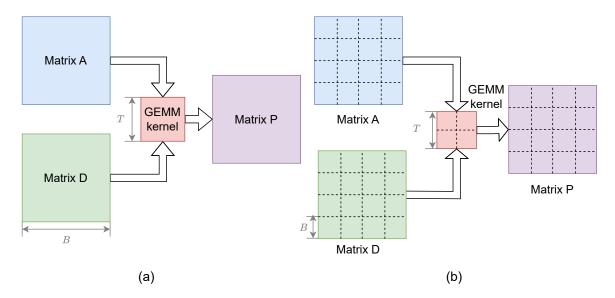

| 5.2  | An example of how the tile size and block size relationship impacts GEMM design          |     |

|      | (a) $B \ge T$ case. (b) $T > B$ case.                                                    | 96  |

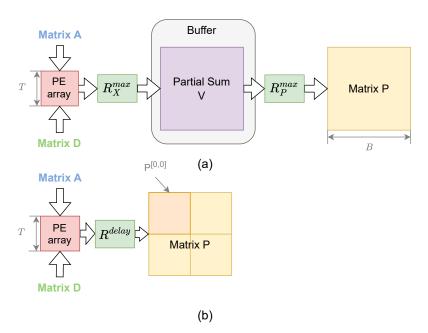

| 5.3  | GEMM kernel design for $B \geq T$ case. (a) The GEMM of maximum calibration              |     |

|      | (b) The GEMM of delayed scaling.                                                         | 98  |

| 5.4  | $B \geq T$ case latency analysis. (a) The matrix multiplication latency of maximum       |     |

|      | calibration. (b) The matrix multiplication latency of the delayed scaling.               | 99  |

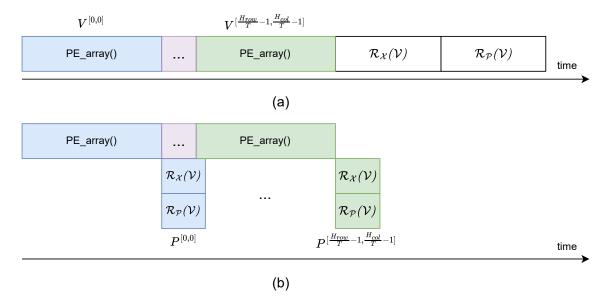

| 5.5  | GEMM kernel design for $T>B$ case. (a) The naive implementation for maximum              |     |

|      | calibration. (b) The pipelined implementation for maximum calibration. (c) The           |     |

|      | implementation of delayed scaling.                                                       | 101 |

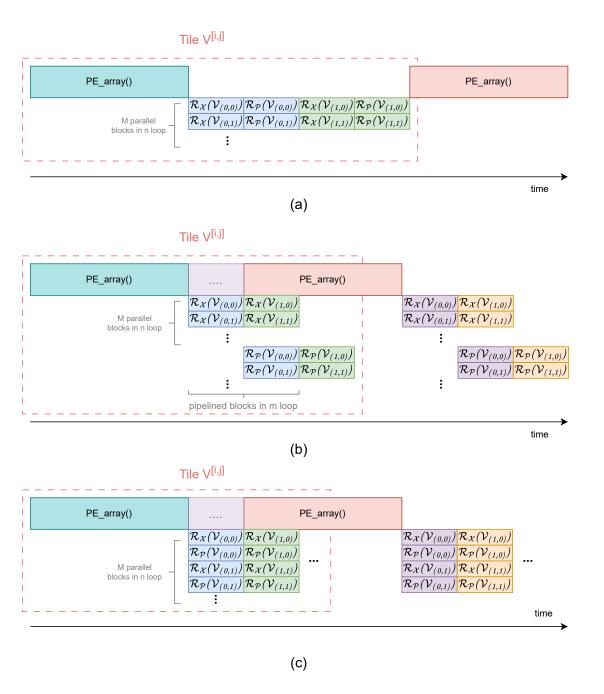

| 5.6  | T>B case latency analysis. (a) The naive matrix multiplication latency of                |     |

|      | maximum calibration. (b) The pipelined matrix multiplication latency of maximum          |     |

|      | calibration. (c) The matrix multiplication latency of the delay update.                  | 102 |

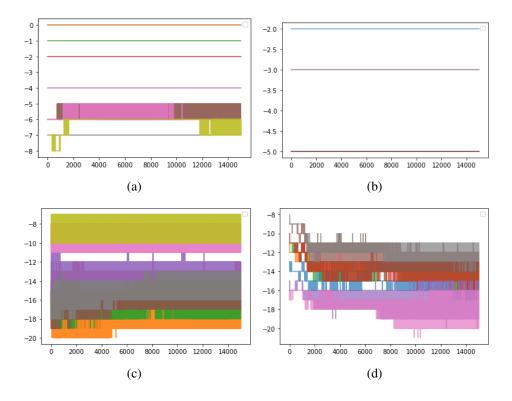

| 5.7  | Block scale values of N-BEATS during training using the maximum calibration              |     |

|      | method. Each subfigure displays the block scale values of the eight fully connected      |     |

|      | (FC) layers within the 29th N-BEATS block in different colors. Training is               |     |

|      | conducted with a global block size. The x-axis indicates the minibatch training          |     |

|      | iteration, while the y-axis represents the block scale value. (a) Activation. (b)        |     |

|      | Weight. (c) Error. (d) Gradient.                                                         | 105 |

| 5.8  | Block scale values of the error tensor during training using the maximum                 |     |

|      | calibration method. The x-axis represents the minibatch training iteration, and the      |     |

|      | y-axis indicates the block scale value. (a) Training with global blocks. (b) Training    |     |

|      | with local blocks (638th block in the first layer).                                      | 106 |

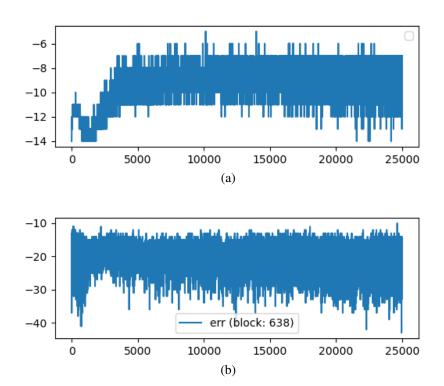

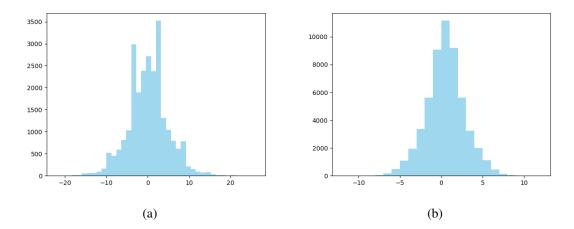

| 5.9  | Histogram of error block scale bias $\Delta X_e$ during training. The x-axis represents  |     |

|      | the $\Delta X_e$ values, and the y-axis indicates the frequency count. (a) Histogram for |     |

|      | Transformer-Tiny. (b) Histogram for ResNet-34.                                           | 111 |

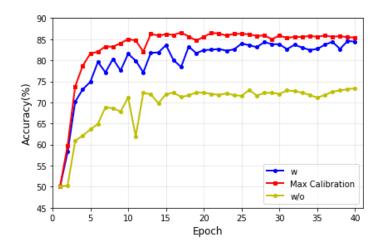

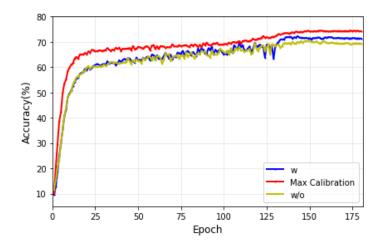

| 5.10 | Accuracy comparison of Transformer-Tiny during training. The block size                  |     |

|      | configuration is $32 \times 32$ .                                                        | 111 |

|      |                                                                                          |     |

xvi List of Figures

| 5.11 | Accuracy comparison of ResNet during training. The block size configuration is |     |  |

|------|--------------------------------------------------------------------------------|-----|--|

|      | $32 \times 32$ .                                                               | 112 |  |

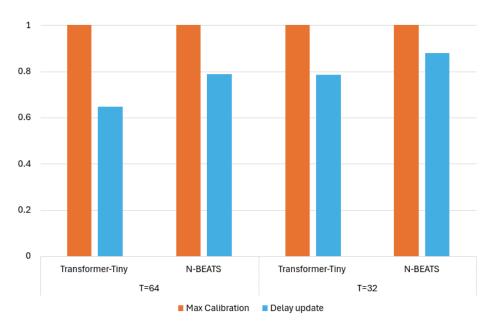

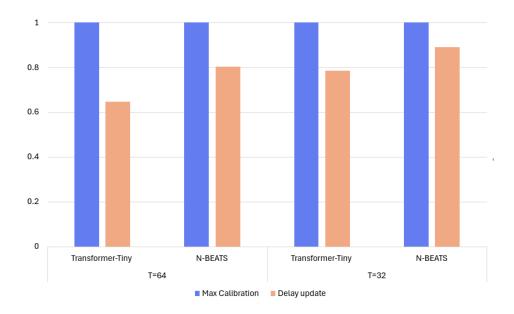

| 5.12 | Normalized training latency comparison using global blocks. The latency of the |     |  |

|      | maximum calibration method is normalized to 1, and the latency of the delay    |     |  |

|      | update method is expressed as a relative ratio.                                | 113 |  |

| 5.13 | Normalized training latency comparison using local blocks. The latency of the  |     |  |

|      | maximum calibration method is normalized to 1, and the latency of the delay    |     |  |

|      | update method is expressed as a relative ratio.                                | 113 |  |

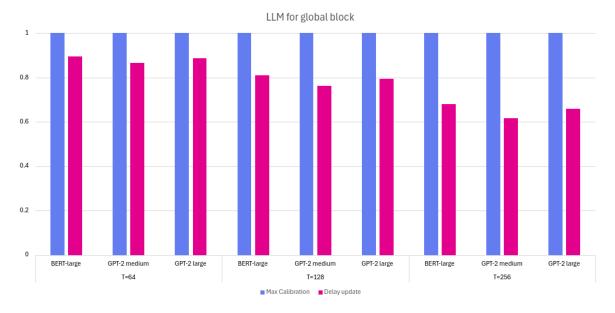

| 5.14 | Normalized training latency comparison using global blocks for large language  |     |  |

|      | model (LLM), including BERT-large and GPT-2 medium/large.                      | 114 |  |

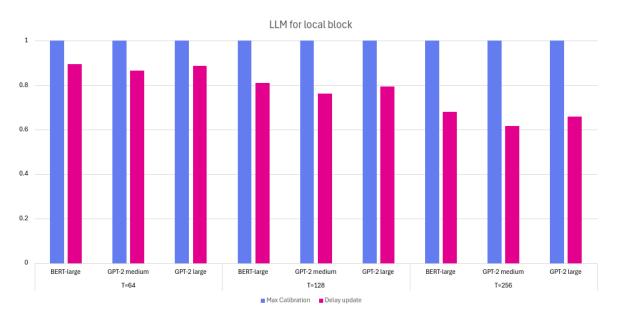

| 5.15 | Normalized training latency comparison using local blocks for large language   |     |  |

|      | model (LLM), including BERT-large and GPT-2 medium/large.                      | 115 |  |

#### CHAPTER 1

#### Introduction

### 1.1 Motivation

In recent years, artificial intelligence (AI) has gained significant traction across a wide range of applications [7, 63, 95, 142]. The success of the AI models, especially deep neural network (DNN), has attracted tremendous investment in developing the latest AI models from private and government departments. In America, the Stargate project, led by private sectors such as OpenAI, Softbank, Oracle, and MGX, was announced to invest up to \$500 billion in the U.S. AI infrastructure, particularly data centers and power generation facilities [69, 136]. Simultaneously, in the Middle East, Saudi Arabia launched Humain, committing \$77 billion to build out graphics processing unit (GPU) clusters and other AI infrastructure, aimed at capturing 7% of global AI training capacity by 2030. The United Arab Emirates (UAE) is also mobilizing significant AI investments via funds such as MGX's \$100 billion asset pool, demonstrating the global scale of strategic AI infrastructure deployment [113].

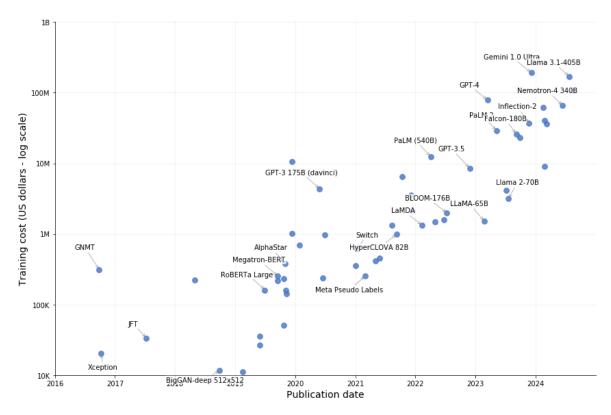

Performance is crucial for the evolution of DNNs, particularly as computational requirements are also surging. For example, the number of parameters of GPT-3 in 2020 was 175 billion; now the new large language model (LLM)s have many more weight parameters [14]: DeepSeek-R1 has 671 billion, Grok has 314 billion, and Llama 3.3 has 405 billion. The most recent LLMs are estimated to have several trillion parameters (GPT-4 has 1.8 trillion and Claude-3 2 trillion) [33]. Along with increasing DNN model scale, the training cost is becoming a new problem for DNN. Reference [111] summarized the training cost of LLMs, and this is reproduced in Figure 1.1.

1

2 1 Introduction

FIGURE 1.1: Estimated training cost of select AI models, 2016-24 (Source: Epoch AI, 2024) [111]

TABLE 1.1: Supported Precision of different NVIDIA GPU architectures [128, 168]

|           | Year | Cuda Core precisions   | Tensor Core precisions          |

|-----------|------|------------------------|---------------------------------|

| Maxwell   | 2014 | FP64/32,INT8           | No                              |

| Pascal    | 2016 | FP64/32/16             | No                              |

| Volta     | 2017 | FP64/32/16, INT8       | FP16                            |

| Ampere    | 2020 | FP64/32/16, INT8, BF16 | FP64/16, BF16, TF32, INT8/4/1   |

| Hopper    | 2022 | FP64/32/16, BF16, INT8 | FP64/16/8, TF32, BF16, INT8     |

| Blackwell | 2024 | FP64/32/16, BF16       | FP64/16/8/6/4, TF32, BF16, INT8 |

A majority of the training cost is associated with the power consumption, including cooling [111]. The power consumption brings both economic and environmental impact, making the energy efficiency of the AI chip a critical factor [33]. One of the critical techniques for energy-efficient training is low-precision arithmetic, which can reduce the memory storage size requirements, memory I/O bandwidth, and increase the on-chip parallelism. Low-precision arithmetic is also one of the key innovations in the evolution of GPUs. As summarized in Table 1.1, the trend is to support more and more lower precision types.

1.1 MOTIVATION 3

Block arithmetic is a promising technique that reduces precision requirements and power consumption. Block arithmetic uses floating-point (FP) or integer format for its data, but the elements within a block have a shared exponent. This method further reduces the word length of the element, and the shared exponent expands their dynamic range. Block arithmetic includes arithmetic like block minifloat (BM), block floating-point (BFP), etc. More recently, block arithmetic has been adopted by the major computer manufacturers, including Microsoft, AMD, Intel, Meta, NVIDIA, and Qualcomm, in the form of the microscaling (MX) format [129, 144]. But some questions for block arithmetic remain:

- Block arithmetic typically operates under low-precision, which can amplify computational errors—particularly in matrix multiplication—thereby affecting training accuracy. In addition, block arithmetic can employ smaller block sizes. Accumulating partial sums across different small blocks may introduce additional rounding errors. Furthermore, to improve accuracy, different precision configurations for forward and backward propagation are often applied during training. What are the optimal arithmetic implementations under these conditions, particularly for matrix multiplication?

- Block arithmetic involves shared exponent calculation during matrix multiplication. Besides, the difference between block size and the general matrix multiplication (GEMM) kernel tile size introduces design challenges for the GEMM kernel. Furthermore, overlapping inner-product computation with rescaling or other blocks' computation latency is desirable. How can these challenges be addressed in GEMM kernel design?

- Rescaling requires computing the maximum absolute value to determine the block scale, followed by conversion to a low-precision format. This process introduces data dependencies that significantly increase latency and buffer requirements. How can these dependencies be broken at the algorithmic level to reduce latency?

- Given the advantages of block arithmetic, what minimum precision can be employed for training without compromising accuracy, and how can the block arithmetic training performance be maximized?

### 1.2 Aims and Contributions

This thesis aims to develop an improved block arithmetic algorithm and implementation methodology. The specific objectives are as follows:

- At the arithmetic level, propose a block arithmetic implementation that minimizes computational error and supports run-time configurable precision.

- At the GEMM kernel level, design a block arithmetic GEMM kernel and incorporate pipelining to overlap block arithmetic computation latency within the GEMM kernel operation or with other neural network computation blocks.

- For rescaling, propose a simplified and efficient algorithm that eliminates data dependencies, thereby reducing computation latency and improving hardware performance.

- At the accelerator level, use neural basis expansion analysis for interpretable time series analysis (N-BEATS) as an example, investigate the lower precision limits for training, and develop hardware—arithmetic co-optimization strategies to enhance training accelerator design.

The hardware implementation platform utilized in this thesis is field programmable gate array (FPGA), a reconfigurable architecture that offers significant flexibility. The arithmetic operations in other platforms—such as central processing unit (CPU), GPU, or application specific integrated circuit (ASIC)s—are fixed in the datapath post-fabrication. The flexibility of FPGAs enables the implementation of accelerators, making it an ideal platform for this research. The contributions of this thesis are summarized as follows:

**BM for inference:** This work presents the first implementation of an FPGA-based accelerator utilizing BM arithmetic during the period of publication. We introduce an integer-based BM arithmetic design to avoid rounding in normalization for inference acceleration. A novel accelerator architecture for N-BEATS is proposed based on a BM systolic array. Experimental results demonstrate that 8-bit BM achieves area and performance comparable to an 8-bit signed

FIGURE 1.2: The contribution and structure of the thesis.

integer (INT8) datapath, while maintaining accuracy levels similar to 16-bit floating-point (FP16) on N-BEATS [199].

**BM for training:** We propose a novel cross-block BM multiply accumulate (MAC) unit that supports independent block and tile sizes, and incorporates a high-precision buffer to enhance accuracy. In addition, we present a new BM GEMM kernel capable of run-time precision configuration, enabling optimal precision selection for forward and backward computations. Together, this is the first FPGA-based mixed-precision neural network training accelerator using 4-bit BM for N-BEATS.

**Rescaling for MX:** We analyze the impact of delayed scaling on GEMM performance and propose a delay update scheme. This method estimates the block scale using the maximum absolute value from the previous minibatch iteration. Empirical evaluations indicate that the delay update scheme achieves accuracy comparable to the maximum calibration method. Quantitative analysis of the performance of GEMM reveals significant hardware advantages, with training latency reductions by up to 40%.

### 1.3 Thesis Structure

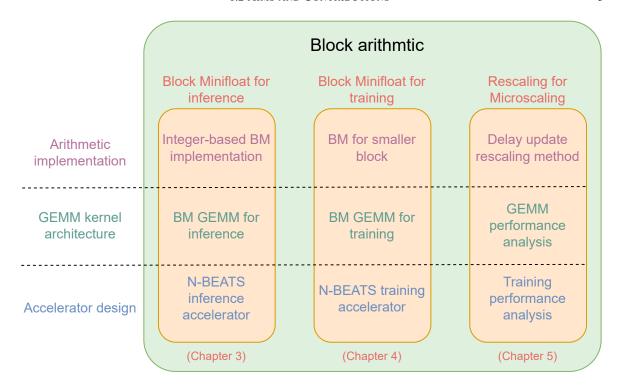

The structure of the thesis is illustrated in Figure 1.2, and each chapter is outlined as follows:

- Chapter 2 provides background information on machine learning and DNN training, a review of relevant literature, and an overview of low-precision arithmetic techniques used in training.

- Chapter 3 presents the implementation of integer-based BM arithmetic, the design of BM GEMM for inference, and the development of an N-BEATS inference accelerator.

- Chapter 4 discusses the implementation of BM arithmetic for smaller blocks in training, the design of BM GEMM for training, and the construction of an N-BEATS training accelerator.

- Chapter 5 analyzes the performance of GEMM, introduces the delay update rescaling method, and evaluates training performance.

- Chapter 6 concludes the thesis and outlines potential directions for future research.

#### CHAPTER 2

### **Background**

This chapter provides an introduction to deep learning and its hardware implementation. It includes a concise overview of foundational concepts in machine learning, DNN, and DNN training, as well as a discussion on low-precision arithmetic for training and hardware platforms for DNN acceleration.

# 2.1 Machine Learning

AI refers to the capability of computer systems to emulate human cognitive functions such as learning and problem-solving. Through AI, a system applies mathematical and logical reasoning to learn from new data and make informed decisions [107].

Machine learning is a subfield of AI that focuses on the development of algorithms capable of improving automatically through experience. A more precise definition of machine learning is provided in [119]:

DEFINITION 2.1.1. A computer program is said to learn from experience E with respect to some class of tasks T and performance measure P, if its performance at tasks in T, as measured by P, improves with experience E.

Task T refers to the specific learning objective that a machine learning algorithm aims to solve, such as image classification, speech recognition, or text generation. Experience E denotes the dataset that provides informative examples from which the algorithm can learn patterns or rules. The performance measure P defines the criteria used to evaluate the effectiveness and generalization capability of the algorithm.

TABLE 2.1: Examples of Machine Learning Tasks

| Task (T)               | Experience (E)              | Performance Measure (P)                    |

|------------------------|-----------------------------|--------------------------------------------|

| Image Classification   | Labeled image datasets      | Classification accuracy                    |

| Speech Recognition     | Audio recordings with       | Accuracy of correctly                      |

|                        | corresponding text labels   | recognized words                           |

| Time Series Prediction | Historical time series      | Forecast bias measured                     |

|                        | data from a specific domain | by metrics such as mean square error (MSE) |

| Text Translation       | Parallel corpora in         | Phrase-level overlap between               |

|                        | two languages               | generated and reference text               |

| Language Modeling      | Text corpora                | Predictive likelihood                      |

|                        |                             | (e.g., perplexity)                         |

For instance, in an image classification task, labeled datasets such as CIFAR-10 [94] and IMAGENET [32] serve as the experience E, while classification accuracy or the cross-entropy loss function are commonly used as performance measures P. A summary of representative machine learning tasks is provided in Table 2.1.

### 2.1.1 Types of Machine Learning

Machine learning algorithms can be categorized based on various criteria. One commonly used classification is based on the type of supervision involved during training [44]. According to this criterion, machine learning algorithms are typically divided into four categories: supervised learning, unsupervised learning, semi-supervised learning, and reinforcement learning.

• Supervised learning. In supervised learning, the training data includes labeled examples that guide the algorithm toward generating correct outputs. The presence of labels enables the system to learn mappings between inputs and desired outputs. Common supervised learning algorithms include k-Nearest Neighbors [24], linear regression [60], logistic regression [60], support vector machine (SVM) [23], decision trees [140], random forests [67], and DNN [47]. A typical example is the image classification task [32], where labeled images are used during training. A *loss function* is employed to evaluate the model's performance; poor predictions result in higher loss values, prompting the algorithm to adjust its parameters accordingly.

- Unsupervised learning. In unsupervised learning, the training data is unlabeled. The algorithm attempts to discover hidden patterns or structures within the data. Representative unsupervised learning algorithms include clustering methods (e.g., K-means [109], hierarchical cluster analysis (HCA) [82]), dimensionality reduction techniques (e.g., principal component analysis (PCA) [83], Kernel PCA [147], locally linear embedding (LLE) [145], t-distributed stochastic neighbor embedding (t-SNE) [106]), and association rule learning algorithms (e.g., Apriori [6], Eclat [188]). A common example is clustering, where data points are grouped into clusters based on similarity, and new data is assigned to the most appropriate cluster.

- Semi-supervised learning. Supervised learning requires a large volume of labeled data, which can be costly and time-consuming to obtain. In contrast, unsupervised learning uses unlabeled data but often suffers from lower accuracy. Semi-supervised learning combines both approaches to mitigate their limitations. It typically involves a small amount of labeled data and a larger pool of unlabeled data. The algorithm initially learns from the labeled data and gradually incorporates the unlabeled data into the training process [149].

- **Reinforcement learning.** Reinforcement learning focuses on decision-making by autonomous agents [174]. During training, the agent interacts with an environment, performs actions, and receives feedback in the form of rewards or penalties. Through repeated interactions, the agent learns an optimal strategy—known as a *policy*—for selecting actions that maximize cumulative rewards. Unlike supervised learning, reinforcement learning does not rely on explicit human guidance or labeled data.

### 2.1.2 Supervised Learning System

A supervised learning system operates in two distinct phases: training and inference. The training phase involves learning generalizable patterns from data, while the inference phase uses the learned parameters to make predictions on previously unseen data.

The training process comprises several key components: the dataset, the model, and the learning algorithm. Typically, the dataset is partitioned into three subsets: training data,

validation data, and test data. The training and validation sets are used during the learning phase, while the test set is reserved for evaluating the final model performance. The machine learning model is a computational framework designed to recognize patterns or make predictions, and it is trained by learning a set of parameters from the data [141]. The learning algorithm iteratively adjusts these parameters to improve prediction accuracy. It consists of an optimization algorithm and a loss function.

To illustrate the training process, consider a linear regression model applied to a time series prediction task. The first step is data preparation, where the dataset is randomly shuffled and divided into training, validation, and test subsets. The training data is used to learn the model, typically forming the majority of the dataset. During training, the model is periodically evaluated on the validation set to monitor overfitting. Overfitting occurs when the model performs well on training data but poorly on validation data. After training, the test set is used to assess the model's generalization performance.

In this example, let  $\mathbf{X} = \{\mathbf{x}_1, \mathbf{x}_2, ..., \mathbf{x}_N\} \in \mathbb{R}^{N \times d_1}$  represent the historical input sequence of N examples, and  $\hat{\mathbf{Y}} = \{\hat{\mathbf{y}}_1, \hat{\mathbf{y}}_2, ..., \hat{\mathbf{y}}_N\} \in \mathbb{R}^{N \times d_2}$  denote the corresponding forecast output sequence. Each input-output pair  $(\mathbf{x}_i, \hat{\mathbf{y}}_i)$  is extracted from a continuous time-series segment of length  $(d_1 + d_2)$ , where the first  $d_1$  elements form the input and the remaining  $d_2$  elements form the output. The resulting datasets are denoted as  $\{\mathbf{X}_{train}, \hat{\mathbf{Y}}_{train}\}$ ,  $\{\mathbf{X}_{valid}, \hat{\mathbf{Y}}_{valid}\}$ , and  $\{\mathbf{X}_{test}, \hat{\mathbf{Y}}_{test}\}$ .

The training process is summarized in algorithm 1. The model takes an input vector  $\mathbf{x}_i$  and predicts an output vector  $\mathbf{y}_i$  using a learnable weight matrix  $\mathbf{w} \in \mathbb{R}^{d_2 \times d_1}$ . After selecting the model hyperparameters  $d_1$  and  $d_2$ , the linear regression model is defined as:

$$\mathbf{y} = f(\mathbf{x}) = \mathbf{w}\mathbf{x}^T \tag{2.1}$$

The mean square error (MSE) is commonly used as the loss function in linear regression. For the i-th training example, the MSE loss is defined as:

$$\mathcal{L}(\hat{\mathbf{y}}_i, \mathbf{y}_i) = \frac{1}{d_2} \|\hat{\mathbf{y}}_i - \mathbf{y}_i\|_2^2 = \frac{1}{d_2} \|\hat{\mathbf{y}}_i - f(\mathbf{x}_i)\|_2^2$$

(2.2)

The loss function [156] quantifies the discrepancy between predicted outputs and ground truth labels. For validation and test data, performance metrics may be identical to the loss function or differ depending on the task. For example, in image classification, cross-entropy loss is used during training, while classification accuracy is used for validation and testing [32]. Common loss functions include MSE [64, 143], cross-entropy [34, 61, 153, 160], and KL divergence [25, 80, 190, 195].

The goal of training is to minimize the loss over the training dataset  $\hat{\mathbf{Y}}_{train}$ :

$$\min_{\mathbf{w}} \sum_{\hat{\mathbf{y}}_i \in \hat{\mathbf{Y}}_{train}} \mathcal{L}(\hat{\mathbf{y}}_i, \mathbf{y}_i)$$

(2.3)

Generalization ability is evaluated on the validation dataset  $\hat{\mathbf{Y}}_{valid}$ :

$$\min_{\mathbf{w}} \sum_{\hat{\mathbf{y}}_i \in \hat{\mathbf{Y}}_{valid}} \mathcal{L}(\hat{\mathbf{y}}_i, \mathbf{y}_i)$$

(2.4)

The optimization algorithm seeks the weight matrix **w** that minimizes the loss function (Equation 2.3). A widely used method is *gradient descent*, a first-order iterative algorithm. The first step involves computing the gradient of the loss with respect to the weights, followed by *weight update*:

$$\mathbf{w}^{(s+1)} = \mathbf{w}^{(s)} - \eta \frac{\partial \mathcal{L}_s}{\partial \mathbf{w}}$$

(2.5)

$\eta$  is the learning rate,  $\frac{\partial \mathcal{L}}{\partial \mathbf{w}}$  is the weight gradient. The gradient computation follows the backpropagation rule:

$$\frac{\partial \mathcal{L}_i}{\partial \mathbf{w}} = \frac{\partial \mathcal{L}_i}{\partial \mathbf{y}_i} \frac{\partial \mathbf{y}_i}{\partial \mathbf{w}} = \frac{2}{d_2} \left| \hat{\mathbf{y}}_i - \mathbf{y}_i \right|^T \cdot \mathbf{x}_i$$

(2.6)

**Algorithm 1:** Learning process for linear regression model. Ep is the training epoch number.

```

// Initialize the weights w, prepare training dataset

\mathbf{X}_{train} and validation dataset \mathbf{X}_{valid}

for Epoch \leftarrow 0 to Ep do

// Training

for x_i, y_i in \{X_{train}, Y_{train}\} do

Forward Computation \mathbf{y}_i = f(\mathbf{x}_i); // Equation 2.1

Training Loss C_i^{train} = \mathcal{L}(\hat{\mathbf{y}}_i, \mathbf{y}_i); // Equation 2.2

Gradient Computation \frac{\partial C_i}{\partial \mathbf{w}}; // Equation 2.6

Weight Update // Equation 2.5

// Validation

for x_i, y_i in \{X_{valid}, Y_{valid}\} do

Inference \mathbf{y}_i = f(\mathbf{x}_i); // Equation 2.1

Validation Loss C_i^{valid} = \mathcal{L}(\hat{\mathbf{y}}_i, \mathbf{y}_i); // Equation 2.2

// Early Stopping

\bar{\mathbf{C}}_{Epoch} = mean(C_i^{valid}) if \bar{\mathbf{C}}_{Epoch} starts diverging then

break;// Stop training

Return weight w

```

During each epoch of the training process, the weight parameters are first updated using the training dataset  $\{\mathbf{X}_{train}, \hat{\mathbf{Y}}_{train}\}$ . The updated weights and the model  $f(\cdot)$  are then evaluated on the validation dataset  $\{\mathbf{X}_{valid}, \hat{\mathbf{Y}}_{valid}\}$ . If the validation loss decreases, the training continues until the final epoch Ep is reached. However, if the average validation loss  $\bar{\mathbf{C}}_{Epoch}$  increases, indicating potential overfitting, the training process is terminated.

### 2.1.3 Deep Neural Network Training

A DNN is a neural network architecture that contains multiple hidden layers between the input and output layers. Commonly used models such as convolutional neural network (CNN) [99], long short-term memory (LSTM) [68], and Transformer [166] are all examples of DNNs.

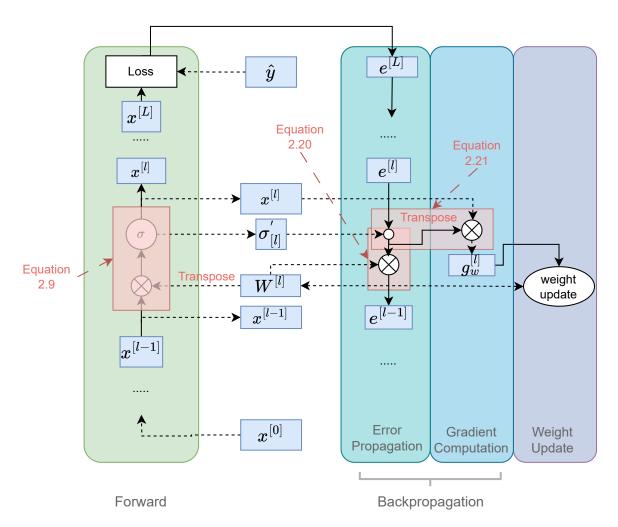

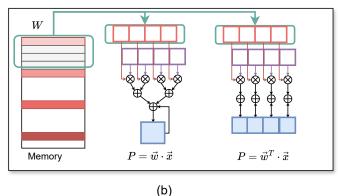

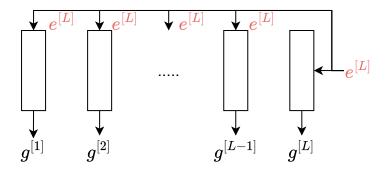

The training process of a DNN is conceptually similar to the time series prediction example, but it employs a layer-wise computation structure, as illustrated in Figure 2.1. The forward

pass, also referred to as inference, transforms the input data through successive layers to produce the output. The backward pass involves propagating the error from the output layer back toward the input layer, allowing the model to update its parameters based on the computed gradients. The gradient of each layer is dependent on the error propagated to that layer.

The overall training procedure of a DNN resembles the process described in algorithm 1, with the forward computation (Equation 2.1) replaced by the forward pass of the DNN, and the gradient computation (Equation 2.6) replaced by the backward pass of the DNN.

A widely used optimization algorithm for DNN training is the stochastic gradient descent (SGD) algorithm [66], which extends the basic gradient descent method used in linear regression. The SGD algorithm can be viewed as a stochastic approximation of gradient descent optimization [154]. Instead of computing gradients over the entire dataset, SGD estimates the gradient using a small subset of training examples  $\{\mathbf{x}_i, \mathbf{x}_{i+1}, ..., \mathbf{x}_{i+B}\}$ , referred to as a *minibatch*. The number of examples in a minibatch, denoted by B, is also known as the *batch size*. Using minibatches introduces stochasticity into the training process, which can have a regularizing effect and lead to more robust gradient estimates [47].

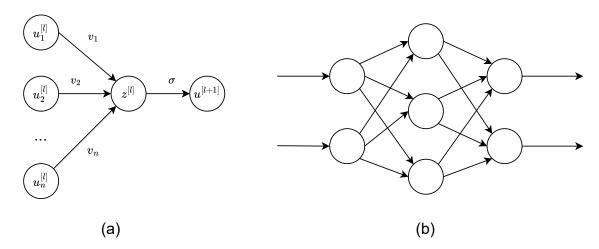

We illustrate the forward and backward passes of a DNN using an multilayer perceptron (MLP) as an example. The MLP is one of the foundational architectures in DNN research and applications [98]. It consists of multiple fully connected (FC) layers, each followed by a nonlinear activation function [120], as depicted in Figure 2.2. The FC layer is a fundamental building block not only in MLPs but also in various widely adopted models, including N-BEATS [130], the feedforward layers in Transformer architectures [166], and other neural components involving matrix multiplication, such as the LSTM cell [68] and self-attention mechanisms in Transformers [166].

#### **Forward Pass**

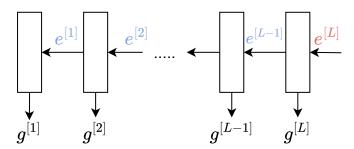

FIGURE 2.1: Forward and backward pass of the *l*-th fully connected (FC) layer in the multilayer perceptron (MLP) example. The left block illustrates the forward pass, while the three blocks on the right represent the backward pass. Solid lines indicate computation flows, and dashed lines denote data read/write operations to memory. Blue blocks represent data that must be stored in memory during forward and backpropagation. Computation blocks are highlighted with semi-transparent red overlays.

Figure 2.2(a) shows layer l with n input neurons. The neuron output  $\mathbf{x}^{[l+1]}$  is the activation function  $\sigma$  output of intermediate value  $\mathbf{z}^{[l]}$ :

$$\mathbf{x}^{[l+1]} = \sigma(\mathbf{z}^{[l]}) \tag{2.7}$$

FIGURE 2.2: a MLP network example. (a) is a n input neuron. (b) is a three-layer MLP network.

where  $\sigma$  is the non-linear activation function, such as rectified linear unit (ReLu), Sigmoid, Tanh functions.  $\mathbf{z}^{[l]}$  equals input vector  $\mathbf{u} = [u_1, u_2, ..., u_n]$  dot product with the weight vector  $\mathbf{v} = [v_1, v_2, ..., v_n]$ :

$$\mathbf{z}^{[l]} = \mathbf{v}\mathbf{u}^T = \sum_{i=0}^n v_i u_i \tag{2.8}$$

A FC layer is composed of multiple neurons and produces multiple outputs for the next layer, as shown in Figure 2.2(b). The computation is a the matrix multiplication of the weight matrix  $\mathbf{W}^{[l]} \in \mathbb{R}^{m \times n}$  with the (l-1)th layer input matrix  $\mathbf{x}^{[l-1]} \in \mathbb{R}^{B \times n}$ :

$$\mathbf{x}^{[l]} = f^{[l]}(\mathbf{x}^{[l-1]}) = \sigma(\mathbf{x}^{[l-1]}\mathbf{W}^{[l]} + \mathbf{b}_{repl}^{[l]})$$

(2.9)

Here  $\mathbf{b}_{repl}^{[l]} \in \mathbb{R}^{B \times m}$ .  $\mathbf{b}^{[l]} \in \mathbb{R}^m$  is the bias vector,  $\mathbf{b}_{repl}^{[l]}$  is achieved by the replication of  $\mathbf{b}^{[l]}$  B times in the first dimension. The input  $\mathbf{x}^{[l-1]}$  is a minibatch of training examples with a batch size of B and each example length of n. And  $\mathbf{z}^{[l]}$  in FC layer is:

$$\mathbf{z}^{[l]} = \mathbf{x}^{[l-1]} \mathbf{W}^{[l]T} + \mathbf{b}_{renl}^{[l]}$$

(2.10)

Thus, a DNN with L layers can be written as:

$$D(\mathbf{x}^{[0]}) = f^{[L]}(\dots f^{[2]}(f^{[1]}(\mathbf{x}^{[0]}))) = \mathbf{x}^{[L]}$$

(2.11)

$\mathbf{x}^{[0]}$  is the input of the network,  $\mathbf{x}^{[L]}$  is the DNN model output.

#### **Backward Pass**

Before computing the backward pass, the output  $\mathbf{x}^{[L]}$  is compared to the label  $\hat{\mathbf{y}}$  using the loss function  $\mathcal{L}$ :

$$C = \mathcal{L}(\mathbf{x}^{[L]}, \hat{\mathbf{y}}) \tag{2.12}$$

In the backward pass, the gradients of each layer are computed according to the backpropagation rule [47], and all weights are subsequently updated using SGD. Backpropagation is a gradient computation algorithm that propagates the error and the gradient of the loss function backward from the output layer toward the input layer by applying the chain rule, as illustrated in Figure 2.1.

In this context, we denote the activation gradient of the l-th layer as the error  $\mathbf{e}^{[l]}$ , and the gradients of the weight and bias parameters in the l-th layer as  $\mathbf{g}_w^{[l]}$  and  $\mathbf{g}_b^{[l]}$ , respectively.

$$\mathbf{e}^{[l]} = \frac{\partial C}{\partial \mathbf{x}^{[l]}} \tag{2.13}$$

$$\mathbf{g}_{w}^{[l]} = \frac{\partial C}{\partial \mathbf{W}^{[l]}} \tag{2.14}$$

$$\mathbf{g}_b^{[l]} = \frac{\partial C}{\partial \mathbf{b}^{[l]}} \tag{2.15}$$

In backpropagation, the error in each layer is computed based on the error propagated from the subsequent layer, while the error in the final layer is derived from the cost function C. Specifically, we define the error at the output layer as  $\frac{\partial C}{\partial \mathbf{x}^{[L]}} = \mathbf{e}^{[L]}$ . Figure 2.3 illustrates the backpropagation process for a DNN layer.

Given the error  $\mathbf{e}^{[l]}$  at the l-th layer, the corresponding gradients— $\mathbf{g}_w^{[l]} \in \mathbb{R}^{m \times n}$  for the weights,  $\mathbf{g}_b^{[l]} \in \mathbb{R}^m$  for the biases—and the error propagated to the (l-1)-th layer,  $\mathbf{e}^{[l-1]} \in \mathbb{R}^{B \times n}$ , are computed as follows:

$$\mathbf{e}^{[l-1]} = \mathbf{e}^{[l]} \frac{\partial \mathbf{x}^{[l]}}{\partial \sigma} \frac{\partial \sigma}{\partial \mathbf{z}^{[l]}} \frac{\partial \mathbf{z}^{[l]}}{\partial \mathbf{e}^{[l]}}$$

(2.16)

$$\mathbf{g}_{w}^{[l]} = \mathbf{e}^{[l]} \frac{\partial \mathbf{x}^{[l]}}{\partial \sigma} \frac{\partial \sigma}{\partial \mathbf{z}^{[l]}} \frac{\partial \mathbf{z}^{[l]}}{\partial \mathbf{W}^{[l]}}$$

(2.17)

$$\mathbf{g}_{b}^{[l]} = \mathbf{e}^{[l]} \frac{\partial \mathbf{x}^{[l]}}{\partial \sigma} \frac{\partial \sigma}{\partial \mathbf{z}^{[l]}} \frac{\partial \mathbf{z}^{[l]}}{\partial \mathbf{b}^{[l]}}$$

(2.18)

$\frac{\partial \sigma}{\partial \mathbf{z}^{[l]}} = 1$ ,  $\sigma_{[l]}^{'} = \frac{\partial \mathbf{x}^{[l]}}{\partial \sigma}$  is the derivative of activation function. If the activation function is ReLu, then:

$$\sigma'_{[l]}(x_i) = \begin{cases} 1 & (x_i > 0) \\ 0 & (x_i \le 0) \end{cases}$$

(2.19)

$x_i$  is the ith element in x. Thus, the error and gradient of lth FC layer are:

$$\mathbf{e}^{[l-1]} = (\mathbf{e}^{[l]} \circ \sigma'_{[l]}) \mathbf{W}^{[l]}$$

(2.20)

$$\mathbf{g}_{w}^{[l]} = \left(\mathbf{e}^{[l]} \circ \sigma_{[l]}^{'}\right)^{T} \mathbf{x}^{[l]}$$

(2.21)

$$\mathbf{g}_b^{[l]} = sum((\mathbf{e}^{[l]} \circ \sigma'_{[l]}), 0) \tag{2.22}$$

We define sum(X, d) as summing each row on the dth dimension of a tensor X. Once the gradient computation finishes, weights and bias will be updated with the SGD algorithm [66]:

$$\mathbf{W}^{[l]} = \mathbf{W}^{[l]} - \eta \mathbf{g}_w^{[l]} \tag{2.23}$$

$$\mathbf{b}^{[l]} = \mathbf{b}^{[l]} - \eta \mathbf{g}_b^{[l]} \tag{2.24}$$

FIGURE 2.3: The forward and backward pass of a FC layer. (a) is the forward pass (inference), (b) is the backward pass.

### 2.2 Literature overview

# **2.2.1** Challenge in Training Acceleration

Unlike inference, training involves both backpropagation and weight updates, making its acceleration fundamentally different from that of inference. First, training requires significantly more computation and memory operations. Second, these computational differences lead to distinct hardware optimization strategies for memory access and processing.

As illustrated in Figure 2.1, training differs from inference in several key aspects [52, 101]:

• Computation. The computational operations are highlighted in semi-transparent red blocks in Figure 2.1. In the FC layer, both forward and backward passes involve matrix multiplications. However, matrix transpositions are required in Equation 2.9

and Equation 2.20, which necessitate either non-unit stride memory access or matrix reorganization in memory. Additionally, different activation functions impose varying computational demands.

- **Data Dependency.** Beyond the layer-wise dependencies present in both forward and backward passes, training introduces additional dependencies. Within each training iteration, backpropagation can only commence after the forward pass and loss computation are complete. Similarly, the forward pass of the next iteration must wait until the current iteration's backpropagation finishes. Within the backward pass of the l-th layer, the weight update for  $\mathbf{W}^{[l]}$  (Equation 2.23) depends on the completion of gradient computation (Equation 2.21), which in turn depends on the error propagation for  $\mathbf{e}^{[l]}$  (Equation 2.20). These dependencies constrain the achievable parallelism.

- **Data Storage.** During the forward pass, in addition to storing the input/output activations of the l-th layer and weights  $\{\mathbf{W}^{[1]},...,\mathbf{W}^{[L]}\}$ , the intermediate activations  $\{\mathbf{x}^{[0]},...,\mathbf{x}^{[L-1]}\}$  and activation derivatives  $\{\sigma'_{[0]},...,\sigma'_{[L-1]}\}$  must also be stored for use in the backward pass. During backpropagation, both the error  $\mathbf{e}^{[l]}$  and the gradient  $\mathbf{g}^{[l]}_w$  must be stored. The memory requirements for storing intermediate results vary depending on the activation function used.

- **Data Movement.** In addition to standard data movement for layer-wise computation and error propagation, training introduces significantly more data transfer than inference. During the forward pass,  $\mathbf{x}^{[l-1]}$  and  $\sigma'_{[l]}$  must be written to memory for use in the backward pass. In the backward pass, the weight update step requires reading both the weight  $\mathbf{W}^{[l]}$  and the gradient  $\mathbf{g}_w^{[l]}$  from memory, followed by writing the updated weight back. In neural networks with FC layers, weights  $\{\mathbf{W}^{[1]}, ..., \mathbf{W}^{[L]}\}$  are typically stored off-chip, necessitating high memory bandwidth to avoid bottlenecks.

Besides the challenges inherent in training, the optimization techniques used for training differ significantly from those used for inference. Methods such as low-precision arithmetic and sparsity are widely adopted in inference acceleration [16, 46, 57, 65, 70, 78, 100, 131, 151]. Many inference accelerators utilize fixed-point number systems due to their reduced hardware area and lower computation latency compared to FP. However, the limited dynamic

range of fixed-point arithmetic is insufficient for training, where FP formats are often required [10, 114, 124].

In sparsity optimization, inference can benefit from weight pruning, which reduces the number of computations by creating sparse weight matrices. In contrast, training involves continuous weight updates in every iteration, making it difficult to maintain the fixed sparse weights throughout the process [101].

#### 2.2.2 Related Works

In response to the aforementioned challenges, numerous studies have proposed solutions aimed at improving training efficiency. This section provides a brief overview of these approaches, categorized by the hardware platforms used—specifically, implementations targeting ASIC and FPGA architectures.

#### **ASIC**

Many DNN applications, particularly those deployed on edge devices, require substantial computational power while meeting strict latency constraints. To enable real-time deployment of DNNs, embedded processors must deliver high throughput with low power consumption. Consequently, the demand for domain-specific accelerators has grown significantly. ASIC architectures, designed for customized applications, offer optimal speed and energy efficiency [108].

Numerous ASIC-based solutions have been proposed to address the challenges outlined above. These approaches can be broadly categorized into two strategies for mitigating the transposition problem in computation. The first approach is data rearrangement for the GEMM kernel input. This method involves reordering matrix indices to produce a transposed matrix as input to the GEMM kernel, as illustrated in Figure 2.4(a). The latency introduced by data rearrangement can be overlapped with computation latency between matrix tiles. References [102, 104] implement this by reading tiled weights from external memory and rearranging the transposed tiles in on-chip static random-access memory (SRAM). Other

FIGURE 2.4: Techniques for addressing the transposition problem. (a) Data rearrangement. (b) Data path configuration. The uncolored/colored bars in the memory block represent elements of W, with word lengths depending on specific applications (e.g., 8-bit or 16-bit).

works [150, 155] propose customized SRAM designs capable of directly reading transposed matrices, albeit at the cost of reduced SRAM cell density. The second approach is the configurable data path inside GEMM kernel. This strategy avoids explicit transposition by designing a configurable data-path GEMM kernel, as shown in Figure 2.4(b). By adjusting the data flow between processing element (PE)s, the PE array can be reconfigured to perform transposed matrix multiplication. However, the performance of the GEMM kernel varies depending on the data path configuration. Reference [152] introduces a PE array that can be configured as weight-stationary, output-stationary, or row-stationary. Reference [102] achieves transposition by switching the weight and output dataflow configurations, while [88] enables transposed/non-transposed computation by altering the input data paths for weights and activations.

To address data dependency challenges, alternative algorithms have been proposed to replace traditional backpropagation. One such method is direct feedback alignment, illustrated in Figure 2.5. In standard backpropagation, each layer's error is computed based on the error from the subsequent layer. In contrast, direct feedback alignment propagates the final layer error  $\mathbf{e}^{[L]}$  directly to all preceding layers, thereby breaking inter-layer dependencies and increasing parallelism in the backward pass. References [52, 56, 102] incorporate direct feedback alignment into ASIC designs to enhance training efficiency. However, these methods are typically effective only for specific problem domains.

Normal Backpropagation

Direct Feedback Alignment

FIGURE 2.5: Illustration of direct feedback alignment.

To mitigate data storage and movement overheads, sparsity introduced by activation functions (e.g., ReLu) or max pooling layers is exploited during backpropagation to compress zero-valued elements in tensors. Techniques such as zero-value compression [86, 91], compressed sparse row encoding [79], and run-length encoding [102] have been proposed. Additional methods include JPEG-based compression and hierarchical compression schemes [38, 85, 132], which build upon run-length encoding. In sparsity optimization, MAC unit designs also leverage sparsity to skip zero-valued computations during backpropagation, thereby improving computational efficiency [52, 86, 91, 102].

#### **FPGA**

A FPGA is a reconfigurable integrated circuit that can be programmed post-fabrication to implement a wide range of custom circuit designs. The architecture of a FPGA consists of various programmable components, including logic elements, I/O modules, and specialized

units. These components are interconnected via pre-fabricated routing tracks and programmable switches. Circuit functionality and reconfiguration are primarily achieved through logic blocks and digital signal processing (DSP) blocks. Developers typically design circuits using hardware description language (HDL) languages such as Verilog or VHDL, or convert high-level C code into HDL. Once the HDL design is complete, a computer aided design (CAD) tool compiles it into a *bitstream* file used to configure the FPGA [12].

The programmability, flexibility, and customizable I/O interfaces make FPGA a compelling platform for deep learning acceleration tasks [11]. First, its fine-grained programmability allows for the implementation of computing units with low-precision or custom data formats, such as INT8, 8-bit floating-point (FP8), binary, or ternary arithmetic [29, 118]. Second, the customization capabilities enable accelerator designs optimized for specific constraints, such as low-latency and low-batch inference scenarios. Third, the reconfigurability of FPGA allows developers to adapt to the rapid evolution of neural network architectures by modifying the HDL design and reloading the bitstream. Fourth, unlike traditional processors, FPGA lacks hierarchical memory and instruction sets, enabling direct data access from I/O interfaces. This feature allows neural network accelerators on FPGA to communicate directly with external devices supplying input data.

Several FPGA-based inference accelerator designs have demonstrated the platform's performance capabilities. For example, reference [176] achieved a 741 MHz operating frequency and over 7 TOPS for CNN inference on a Xilinx Ultrascale device, while reference [35] reported 17.2 TOPS on a Xilinx Alveo U280 at 300 MHz. Furthermore, FPGA can integrate multiple IP cores to support full-system implementations. These high-performance results also suggest the feasibility of on-chip training using FPGA.

Recent research has explored FPGA implementations for training. Early works investigated architectural and parallelism strategies for CNN training [105, 198]. References [123, 193] focused on implementing BFP-based training for CNN, while [41] demonstrated 8-bit BFP training using the stochastic weight averaging low-precision (SWALP) algorithm, achieving accuracy comparable to 32-bit floating-point (FP32). Reference [167] showed that low-batch training significantly reduces memory requirements and improves energy efficiency on FPGA

compared to GPU. Reference [172] proposed a hybrid model-layer parallelism strategy for CNN training, achieving 6.4× higher energy efficiency than comparable GPU servers. These implementations highlight the energy efficiency advantages of FPGA, making it well-suited for power-constrained, edge-based training applications.

# 2.3 Low-precision arithmetic used for training

Low-precision arithmetic is one of the key optimization techniques for neural network training. Its primary advantage lies in reducing memory usage for both on-chip and off-chip storage, thereby lowering memory bandwidth requirements. A variety of low-precision arithmetic schemes have emerged, including Minifloat, posit [51], block arithmetic, mixed fixed-point, and logarithmic number systems [196, 197]. Among these, Minifloat and block arithmetic are the two most widely adopted approaches in training.

#### 2.3.1 Fixed Point

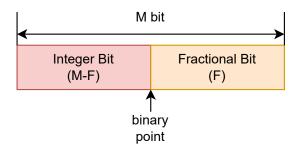

Fixed-point arithmetic is a method of representing real numbers in digital systems. It encodes values using a fixed number of binary digits, with a predetermined position for the binary point. An example of an unsigned fixed-point number is shown in Figure 2.6. A fixed-point number with M total bits and F fractional bits can be represented as a bit vector:

$$U = (u_{M-1}u_{M-2}\dots u_0), \quad u_i \in \{0, 1\}$$

(2.25)

Its numerical value is given by:

$$U = (u_{M-1}u_{M-2}\dots u_0)_2 = \sum_{i=0}^{M-1} u_i \times 2^i \times 2^{-F}$$

(2.26)

FIGURE 2.6: Unsigned fixed-point arithmetic scheme.

Fixed-point numbers can also represent signed values using two's complement notation. In this format, the most significant bit (most significant bit (MSB)) carries a negative weight, resulting in the following representation for a signed fixed-point number S:

Further, the fixed point can also represent a signed real number in 2's complement form. The representation of the 2's complement form is similar to the unsigned fixed-point, but with the MSB having weight of  $-u_{M-1}2^{M-1}$ . Thus, the 2's complement form of a signed fixed-point number S can be represented as:

$$S = (s_{M-1}s_{M-2}s_{M-3}...s_0)_2 = (-s_{M-1}2^{M-1} + \sum_{i=0}^{M-2}s_i \times 2^i) \times 2^{-F}, s_i \in \{0, 1\} \quad (2.27)$$

The precision and dynamic range of a fixed-point number depend on the configuration of integer and fractional bits. For a signed fixed-point number with m total bits and f fractional bits, the smallest representable difference between two values is  $2^{-f}$ , and the roundoff error introduced during quantization is approximately  $2^{-f-1}$ .

The dynamic range of such a number is given by:

$$-2^{m-f-1}, 2^{m-f-1} - 2^{-f}$$

(2.28)

If the magnitude of a real number exceeds this range, overflow or underflow occurs. A common mitigation strategy is saturation, where values are clipped to the maximum or minimum representable limits, introducing clipping errors.

Due to its limited dynamic range, fixed-point arithmetic has traditionally seen limited use in training [21]. However, some works have explored fixed-point-based training by incorporating

| Sign  | exponent | mantissa |

|-------|----------|----------|

| (S)   | (E)      | (M)      |

| 1 bit | x bit    | y bit    |

FIGURE 2.7: FP arithmetic structure

scaling factors or shared exponents to extend the dynamic range [18, 54, 55, 92, 164, 187]. These approaches are conceptually closer to block arithmetic than to conventional fixed-point representations. However, fixed-point arithmetic can be highly efficient for inference when specific techniques are applied to address quantization challenges. SmoothQuant [180] introduces a post-training quantization method for LLM, enabling INT8 quantization of both weights and activations across all matrix multiplications in LLMs. Building on SmoothQuant, FlightLLM [189] achieves an average of 3.5 bits for weights and 8 bits for activations.

## **2.3.2 Floating Point**

FP arithmetic is widely used in neural network training due to its significantly larger dynamic range compared to fixed-point arithmetic. The IEEE 754 standard [73] defines the conventional formats for FP representation. A floating-point number can be expressed in the format FP $\langle x,y\rangle$ , where the number consists of a 1-bit sign S, an x-bit exponent E, and a y-bit mantissa M, as illustrated in Figure 2.7.

The IEEE 754 standard specifies three commonly used FP formats: 64-bit floating-point (FP64), FP32, and FP16. Specifically, FP64 uses a 64-bit  $FP\langle11,52\rangle$  format, FP32 uses a 32-bit  $FP\langle8,23\rangle$  format, and FP16 uses a 16-bit  $FP\langle5,10\rangle$  format. These formats are widely supported by modern GPU architectures, such as NVIDIA A100 [126] and H100 [127], and have been adopted in early training implementations [89, 115], which primarily utilize FP32 and FP16.

|            | Format   | Bit Length | Data Format                |

|------------|----------|------------|----------------------------|

| IEEE 754   | FP64     | 64         | $FP\langle 11, 52 \rangle$ |

| Standard   | FP32     | 32         | $FP\langle 8, 23 \rangle$  |

| Standard   | FP16     | 16         | $FP\langle 5, 10 \rangle$  |

|            | BFloat16 | 16         | $FP\langle 8,7\rangle$     |

|            | FP8      | Q          | $FP\langle 5,2\rangle$     |

| Minifloat  | 110      | O          | $FP\langle 4,3\rangle$     |

| Willinioat | FP6      | 6          | $FP\langle 2,3\rangle$     |

|            | 110      | U          | $FP\langle 3,2\rangle$     |

|            | FP4      | 4          | $FP\langle 2,1\rangle$     |

TABLE 2.2: The summary of floating point data format

The value of IEEE 754 standard FP number f(s, e, m) is given by Equation 2.29: