# Matching Properties and Applications of Compatible Lateral Bipolar Transistors (CLBTs)

Hiu Yung WONG B.Eng.

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of Master of Philosophy

in

the Computer Science and Engineering Department

©The Chinese University of Hong Kong July, 2001

The Chinese University of Hong Kong holds the copyright of this thesis. Any person(s) intending to use a part or the whole of the materials in this thesis in a proposed publication must seek copyright release from the Dean of the Graduate School.

# Matching Properties and Applications of Compatible Lateral Bipolar Transistors (CLBTs)

submitted by

#### Hiu Yung WONG

for the degree of Master of Philosophy at The Chinese University of Hong Kong in July 2001

## Abstract

As System-On-a-Chip (SOC) and mixed-signal technologies become increasingly popular, realization of Bipolar Junction Transistors (BJTs) and Metal-Oxide-Semiconductor Field Effect Transistors (MOSFETs) on the same chip has also increased in importance. This is because BJTs and MOSFETs are well-known for their superior properties in implementing high speed analog and low power digital circuits respectively. Since no additional processing steps are required, Compatible Lateral Bipolar Transistors (CLBTs), which are parasitic lateral BJTs formed in Complementary Metal-Oxide-Semiconductor (CMOS) processes, provide an inexpensive means and alternative to BiCMOS processes.

At the same time, deep submicron and low-power ICs put more stringent requirements on the matching properties of the devices, especially in analog circuits. Matching properties refer to the degree of similarity between electrical parameters of two identically designed and used devices. MOSFETs are notorious for their poor matching properties in subthreshold conduction and CLBTs are generally expected to have better matching properties. In this thesis, the matching properties of CLBTs and MOSFETs fabricated using a typical digital IC process have been studied and compared systematically and quantitatively, in the hope of providing useful data for circuit designers. Test

chips containing arrays of pnp CLBTs and nMOSFETs were fabricated using the AMI-ABN 1.5 $\mu m$  n-well process. In an n-well process, only pnp CLBTs can be fabricated and their matching properties were compared with those of nMOSFETs, which are optimized in such a process. The arrays were designed for a good balance between the number of devices, number of available pins and accuracy. Shift registers and transmission gates were used to select individual devices for testing. To emulate a practical condition, the pnp CLBTs were cascoded with pMOSFETs and surrounded with p-type guard rings and designed to have similar layout area as that of the nMOSFETs for fair comparisons. Each chip contained 144 pnp CLBTs and 225 nMOSFETs, giving a total of 576 pnp CLBTs and 900 nMOSFETs in 4 chips.

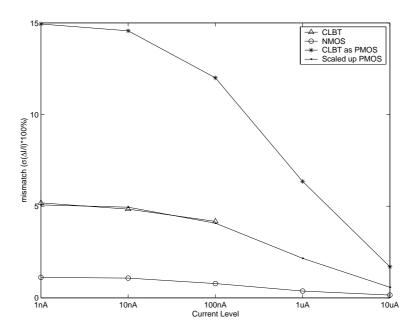

Individual pnp CLBTs under the same biasing conditions were tested at nominal collector current levels from 100nA down to 1nA. The drain currents at levels ranging from  $10\mu A$  down to 1nA of individual pMOSFETs (CLBTs operating in MOS mode) and nMOSFETs were also measured. The matching properties of the devices at different current levels were then calculated. It was found that the matching properties of the nMOSFETs were 3-4 times better than those of the pnp CLBTs and the latter were, in turn, about 3 times better than those of the pMOSFETs. By applying the Law of Area, it was estimated that pMOSFETs with similar layout area as that of the pnp CLBTs would show similar matching properties as the pnp CLBTs. The devices were also paired up as current mirrors and they showed similar matching results.

# Acknowledgments

Thanks to the society, for people working very hard in other areas so that I have the chance to have research as my career.

Thanks to my dearest parents, for supporting me for no reasons.

Thanks to my supervisor, Dr. Philip H.W. Leong, for giving me the opportunities to conduct this research and teaching me knowledge and skills in conducting research. He also provided the Magic layouts of the chip frame and shift register cell and designed the  $I^2C$  test board. Most importantly, he reviewed all the layouts of the test chips and this thesis carefully.

Thanks to Prof. C.F. Chan and Prof. David Y.L. Wu for giving various advice in writing the thesis.

Thanks to Miss Wing-seung Yuen, Mr. Simon Wong, and Mr. Oscar Ma for helping in making the PCB board for chip testing.

Thanks to Dr. Andr $\acute{e}$  van Schaik for proposing the design of the second CLBT test array and various helps and advice on the design of CLBTs in private emails.

Thanks to Dr. Douglas A. Kerns for suggesting the inclusion of the guard

rings in CLBTs for fair comparison in the early stage of this thesis and allowing me to access his Ph.D. thesis for references.

Thanks to Dr. Paul Hasler for reviewing the Magic layout of the Floating-Gate CLBTs and tunnelling and hot electron injection circuits for us.

Thanks to Mr. Kim-wai Law for helping in preparing the photomicrograph of the chip.

Thanks to Mr. Norris Leong, Mr. Ray Chung, and Mr. Ivan Leung, Miss Polly Wan and Mr. Cliff Sze, for giving me various advice and supports in writing the thesis.

Finally, I would like to thank Miss Joyce Ng for reviewing the whole thesis carefully. I would also like to thank Mr. Chuen-fung Wong, Mr. Eric Kwok and Miss Wing-seung Yuen for reviewing some of the chapters and Miss Li-hua Dong and Mr. Chuen-fung Wong for reviewing the Chinese abstract.

# Contents

| A  | bstra                 | $\mathbf{ct}$ |                                                |    |                  | i   |

|----|-----------------------|---------------|------------------------------------------------|----|------------------|-----|

| A  | cknov                 | wledgme       | nts                                            |    |                  | iii |

| Li | ist of                | Figures       |                                                |    |                  | ix  |

| Li | ist of                | st of Tables  |                                                |    | iii  ix  xiii  1 |     |

| 1  | $\operatorname{Intr}$ | oduction      | n                                              |    |                  | 1   |

|    | 1.1                   | Motivati      | on and Objectives                              |    |                  | 1   |

|    | 1.2                   | Contribu      | ntions                                         |    |                  | 3   |

|    | 1.3                   | Organiza      | ation of the Thesis                            |    |                  | 4   |

| 2  | Dev                   | ices and      | Fabrication Processes                          |    |                  | 5   |

|    | 2.1                   | Introduc      | tion                                           |    |                  | 5   |

|    | 2.2                   | BJTs .        |                                                |    |                  | 6   |

|    |                       | 2.2.1         | tructure and Modeling of BJTs                  |    |                  | 6   |

|    |                       | 2.2.2         | tandard BJT Process and BJT Characteristics    |    |                  | 7   |

|    | 2.3                   | MOSFE         | Ts and Complementary MOS (CMOS)                |    |                  | 8   |

|    |                       | 2.3.1         | tructure and Modeling of MOSFETs               |    |                  | 8   |

|    |                       | 2.3.2         | tandard $n$ -well CMOS Process and MOSFETs Cha | ra | և <b>C</b> −     |     |

|    |                       | t             | eristics                                       |    |                  | 11  |

|    | 2.4                   | BiCMOS        | S Technology                                   |    |                  | 13  |

|   | 2.5                    | Summary                                                            | 14    |

|---|------------------------|--------------------------------------------------------------------|-------|

| 3 | Mat                    | tching Properties                                                  | 15    |

|   | 3.1                    | Introduction                                                       | 15    |

|   | 3.2                    | Importance of Matched Devices in IC Design                         | 15    |

|   |                        | 3.2.1 What is Matching?                                            | 15    |

|   |                        | 3.2.2 Low-power Systems                                            | 16    |

|   |                        | 3.2.3 Device Size Downward Scaling                                 | 16    |

|   |                        | 3.2.4 Analog Circuits and Analog Computing                         | 17    |

|   | 3.3                    | Measurement of Mismatch                                            | 18    |

|   |                        | 3.3.1 Definitions and Statistics of Mismatch                       | 18    |

|   |                        | 3.3.2 Types of Mismatches                                          | 20    |

|   |                        | 3.3.3 Matching Properties of MOSFETs                               | 23    |

|   |                        | 3.3.4 Matching Properties of BJTs and CLBTs                        | 27    |

|   | 3.4                    | Summary                                                            | 30    |

| 4 | $\mathbf{C}\mathbf{M}$ | OS Compatible Lateral Bipolar Transistors (CLBTs)                  | 31    |

|   | 4.1                    | Introduction                                                       | 31    |

|   | 4.2                    | Structure and Operation                                            | 32    |

|   | 4.3                    | DC Model of CLBTs                                                  | 34    |

|   | 4.4                    | Residual Gate Effect in Accumulation                               | 35    |

|   | 4.5                    | Main Characteristics of CLBTs                                      | 37    |

|   |                        | 4.5.1 Low Early Voltage                                            | 37    |

|   |                        | 4.5.2 Low Lateral Current Gain at High Current Levels              | 38    |

|   |                        | 4.5.3 Other Issues                                                 | 39    |

|   | 4.6                    | Enhanced CLBTs with Cascode Circuit                                | 40    |

|   | 4.7                    | Applications                                                       | 41    |

|   | 4.8                    | Design and Layout of CLBTs                                         | 42    |

|   | 4.9                    | Experimental Results of Single $pnp$ CLBT, $n$ MOSFET and $p$ MOSF | ET 44 |

|   |                        | 4.9.1 CLBT Gains                                                   | 46    |

|   |                                       | 4.9.2   | Gate Voltage Required for Pure Bipolar Action           | 47 |  |

|---|---------------------------------------|---------|---------------------------------------------------------|----|--|

|   |                                       | 4.9.3   | I-V and Other Characteristics of Bare $pnp$ CLBTs $$    | 49 |  |

|   |                                       | 4.9.4   | Transfer Characteristics of a Cascoded $pnp$ CLBT       | 50 |  |

|   |                                       | 4.9.5   | Transfer Characteristics of an $n$ MOSFET               | 51 |  |

|   |                                       | 4.9.6   | Transfer Characteristics of Cascoded and Bare CLBTs     |    |  |

|   |                                       |         | Operating as $p$ MOSFETs                                | 52 |  |

|   | 4.10                                  | Summ    | ary                                                     | 53 |  |

| 5 | Experiments on Matching Properties 54 |         |                                                         |    |  |

|   | 5.1                                   | Introd  | uction                                                  | 54 |  |

|   | 5.2                                   | Objec   | tives                                                   | 55 |  |

|   | 5.3                                   | Techn   | ology                                                   | 57 |  |

|   | 5.4                                   | Design  | n of Testing Arrays                                     | 57 |  |

|   |                                       | 5.4.1   | nMOSFET Array                                           | 57 |  |

|   |                                       | 5.4.2   | pnp CLBT Array                                          | 59 |  |

|   | 5.5                                   | Design  | of Input and Output Pads (I/O Pads) $\dots \dots$       | 62 |  |

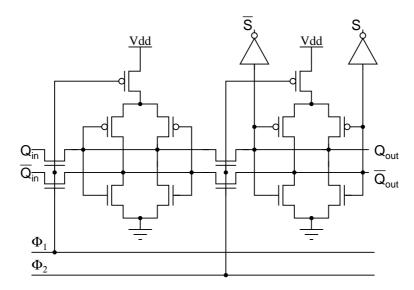

|   | 5.6                                   | Shift I | Register                                                | 62 |  |

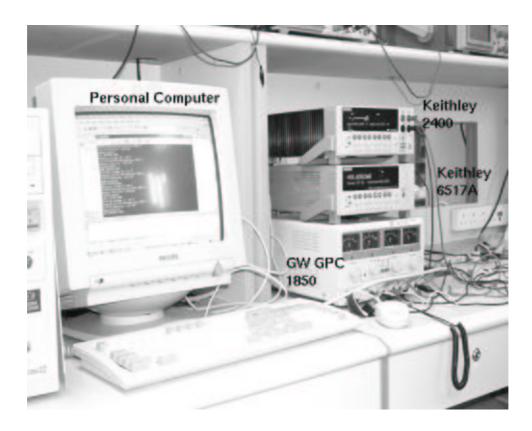

|   | 5.7                                   | Exper   | imental Equipment                                       | 63 |  |

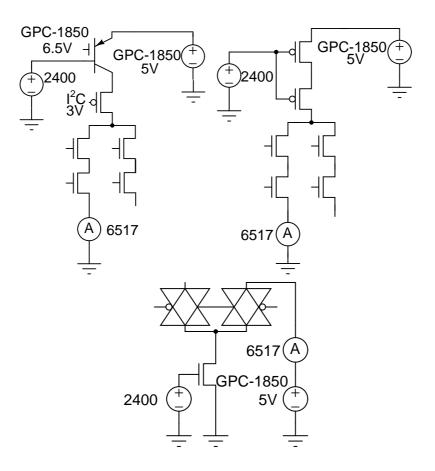

|   | 5.8                                   | Exper   | imental Setup for Matching Properties Measurements      | 65 |  |

|   |                                       | 5.8.1   | Setup for Measuring the Mismatches of the Devices       | 65 |  |

|   |                                       | 5.8.2   | Testing Procedures                                      | 68 |  |

|   |                                       | 5.8.3   | Data Analysis                                           | 68 |  |

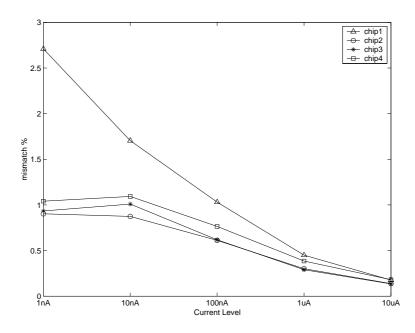

|   | 5.9                                   | Match   | ing Properties                                          | 69 |  |

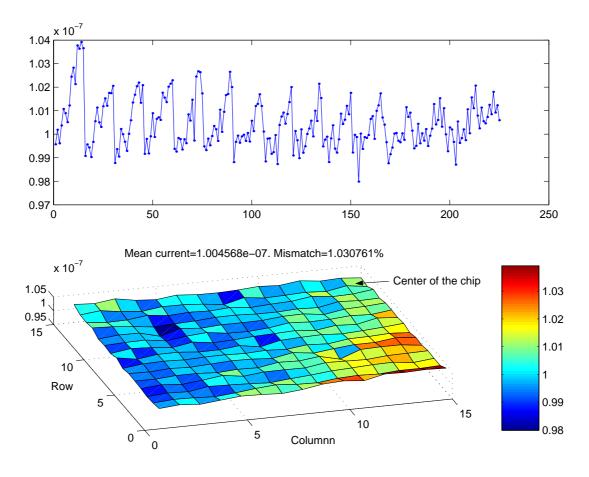

|   |                                       | 5.9.1   | Matching Properties of $n$ MOSFETs                      | 69 |  |

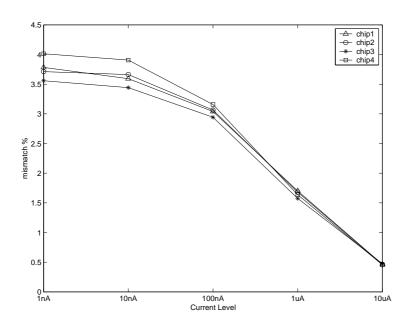

|   |                                       | 5.9.2   | Matching Properties of CLBTs                            | 71 |  |

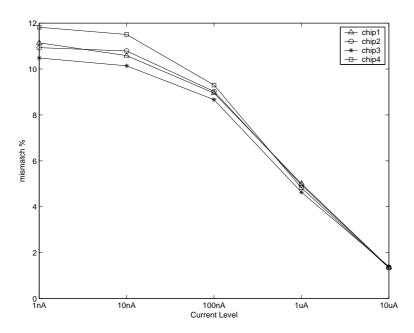

|   |                                       | 5.9.3   | Matching Properties of $p$ MOSFETs                      | 73 |  |

|   |                                       | 5.9.4   | Comments on the Matching Properties of CLBT, $n$ MOSFET | Γ, |  |

|   |                                       |         | and pMOSFET                                             | 76 |  |

| Bi           | bliog         | raphy 1                                                        | 04 |

|--------------|---------------|----------------------------------------------------------------|----|

| D            | $\mathbf{AM}$ | I-ABN $1.5\mu m$ $n$ -well Process Parameters (Second Batch) 1 | 01 |

| $\mathbf{C}$ | $\mathbf{AM}$ | I-ABN 1.5 $\mu m$ n-well Process Parameters (First Batch)      | 98 |

|              | В.3           | Summary                                                        | 97 |

|              |               | B.2.6 Experimental Results of the FGOTA                        | 96 |

|              |               | B.2.5 Experimental Results of the OTA                          | 94 |

|              |               | B.2.4 Hot Electron Injection                                   | 94 |

|              |               | B.2.3 Electron Tunnelling                                      | 93 |

|              |               | B.2.2 Floating Gate CLBTs                                      | 92 |

|              |               | B.2.1 Residual Gate Effect and Collector Current Modulation .  | 89 |

|              |               | patible Lateral Bipolar Transistors (FG-CLBTs)                 | 87 |

|              | B.2           | Trimmable Transconductance Amplifier using Floating Gate Com-  |    |

|              | B.1           | Introduction                                                   | 87 |

| В            | A T           | rimmable Transconductance Amplifier                            | 87 |

|              | A.4           | Summary                                                        | 86 |

|              | A.3           | Hot Electron Effect                                            | 85 |

|              | A.2           | Tunnelling                                                     | 83 |

|              | A.1           | Floating Gate                                                  | 82 |

| A            | Floa          | ting Gate Technology                                           | 82 |

| 6            | Con           | clusion                                                        | 80 |

|              | 5.10          | Summary                                                        | 79 |

|              |               |                                                                | 77 |

|              |               | 5.9.5 Mismatch in CLBT, $n$ MOSFET, and $p$ MOSFET Cur-        |    |

# List of Figures

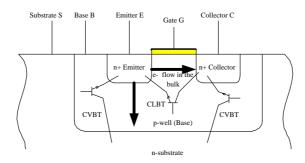

| 1.1 | Cross-sectional view of CLBT                                         |

|-----|----------------------------------------------------------------------|

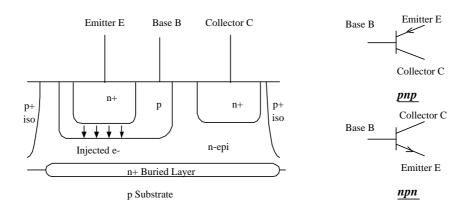

| 2.1 | Cross-sectional view of vertical $npn$ bipolar transistor (left) and |

|     | npn and pnp bipolar transistor symbols (right)                       |

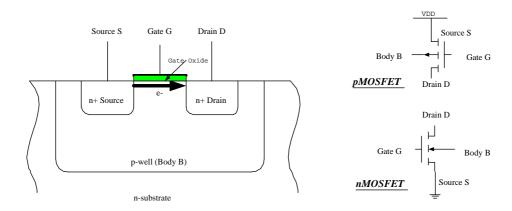

| 2.2 | Cross-sectional view of an $n$ MOSFET (left) and the symbols for     |

|     | nMOSFET and $p$ MOSFET transistors (right) 9                         |

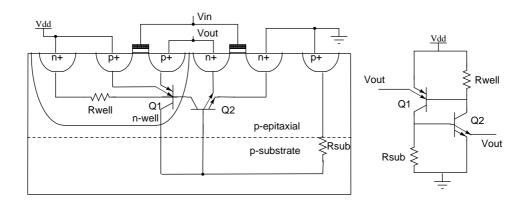

| 2.3 | Cross-sectional view of an <i>n</i> -well CMOS process with latch-up |

|     | circuit identified (left) and the extracted model of the latch-up    |

|     | circuit (right) (adapted from [KL99])                                |

| 3.1 | Common-centroid layout constructed with 4 unit devices con-          |

|     | nected as QUAD. Transistor T1=Tr1+Tr4, transistor T2=Tr2+Tr3. 21     |

| 3.2 | Interdigitated finger layout of transistors Tr1 and Tr2 26           |

| 4.1 | The cross-section of an $npn$ CLBT with parasitic bipolar tran-      |

|     | sistors identified (left) and symbols for $npn$ and $pnp$ CLBTs      |

|     | (right)                                                              |

| 4.2 | Transfer characteristics from source to drain of an $n$ MOSFET       |

|     | when $V_B$ and $V_D$ kept at $Gnd$ and $Vdd$ respectively (adapted   |

|     | from [Arr89])                                                        |

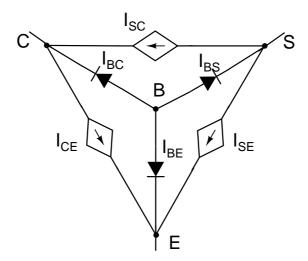

| 4.3 | First order Ebers-Moll model for $npn$ CLBT                          |

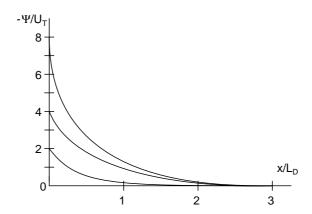

| 4.4  | Electrostatic potential $\psi$ as a function of normalized $x$ to Debye     |    |

|------|-----------------------------------------------------------------------------|----|

|      | length $L_D$ . The surface potential $\psi_S$ is $-2, -4, -8$ $U_T$ respec- |    |

|      | tively (adapted from [Arr89])                                               | 37 |

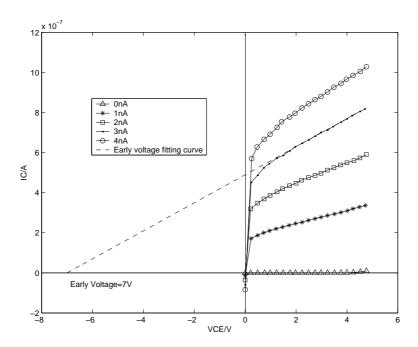

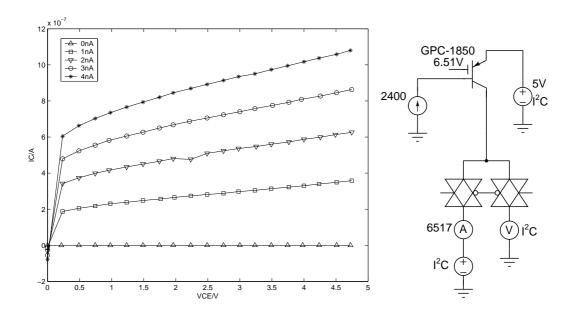

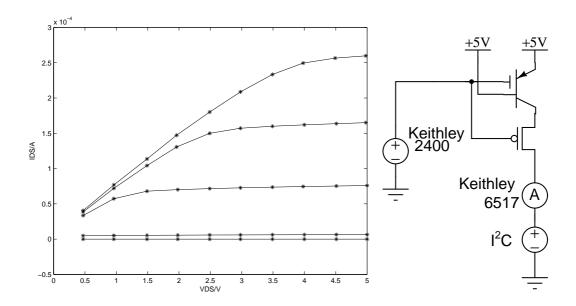

| 4.5  | The current-voltage characteristics of a $pnp$ CLBT fabricated              |    |

|      | using AMI-ABN 1.5 $\mu m$ n-well CMOS process without cascode.              |    |

|      | The Early voltage is about $7V$                                             | 38 |

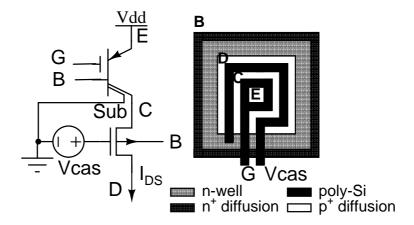

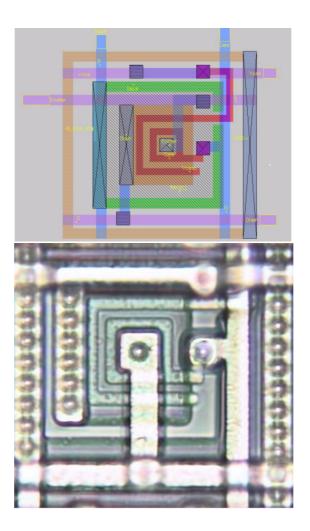

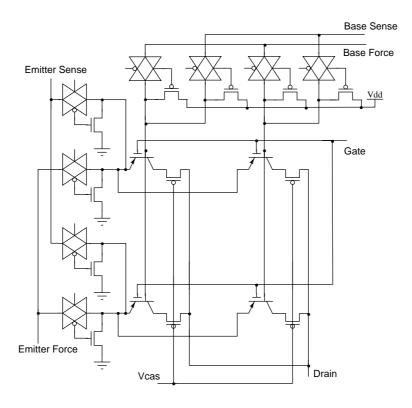

| 4.6  | Structure (left) and layout (right) of cascoded $pnp$ CLBT                  | 40 |

| 4.7  | Magic layout (top) and the photomic<br>rograph (bottom) of a $pnp$          |    |

|      | CLBT cell with cascoded circuit. The outermost ring is the                  |    |

|      | guard ring connected to $Gnd$                                               | 43 |

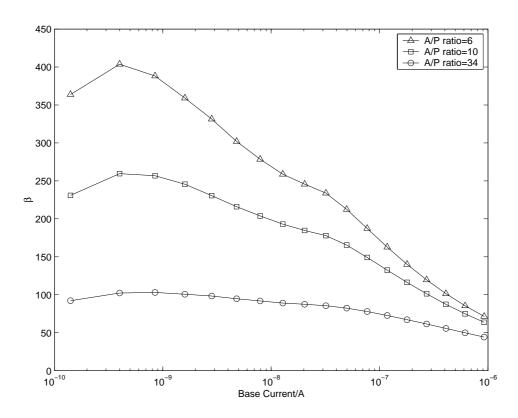

| 4.8  | Current gains of bare $pnp$ CLBTs with different Area-to-Periphery          |    |

|      | (A/P) ratio                                                                 | 46 |

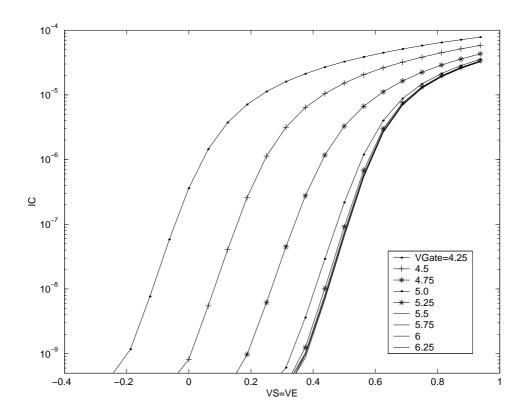

| 4.9  | Transfer Characteristics from source to drain as a function of              |    |

|      | Vs-Vb                                                                       | 47 |

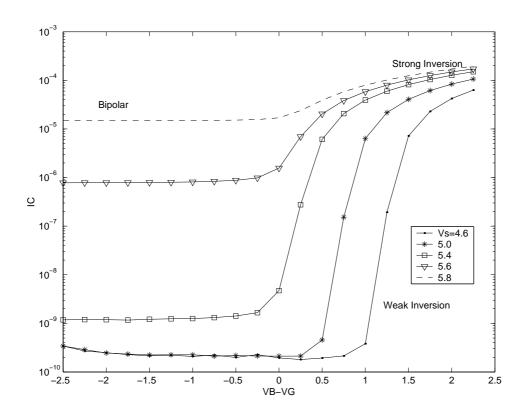

| 4.10 | Transfer Characteristics from source to drain as a function of              |    |

|      | Vb-Vg                                                                       | 48 |

| 4.11 | Transfer characteristics of bare CLBTs (left) and the measure-              |    |

|      | ment setup (right)                                                          | 49 |

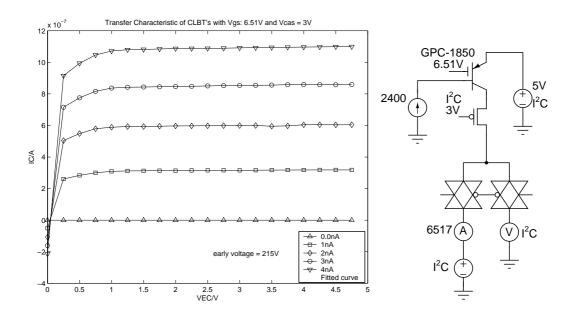

| 4.12 | Transfer characteristics of cascoded CLBTs (left) and the mea-              |    |

|      | surement setup (right)                                                      | 50 |

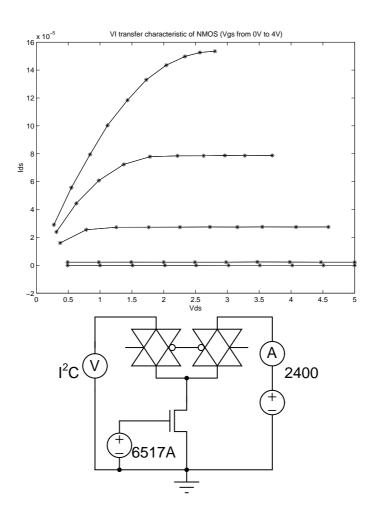

| 4.13 | Transfer Characteristics of $n$ MOSFET (top) and the measure-               |    |

|      | ment setup (bottom)                                                         | 51 |

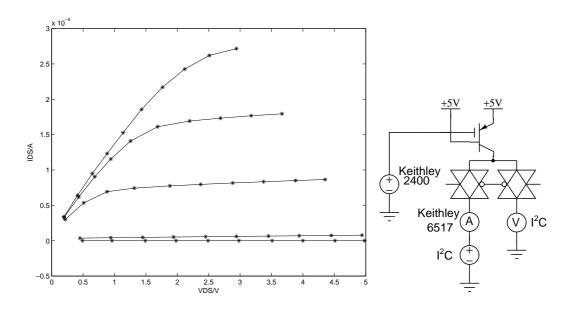

| 4.14 | Transfer characteristics of bare CLBT operating as $pMOSFET$                |    |

|      | at $V_{GS}$ from $0V$ to $4V$ (left) and the measurement setup (right).     | 52 |

| 4.15 | Transfer characteristics of cascoded CLBT operating as $p {\rm MOSFET}$     |    |

|      | at $V_{GS}$ from $0V$ to $4V$ (left) and the measurement setup (right).     | 53 |

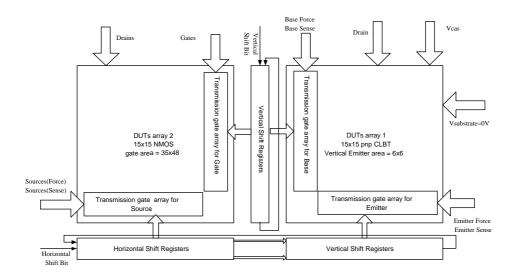

| 5.1  | Top structure of the first batch matching properties test chips             |    |

|      | (array 1 was modified in the second batch)                                  | 55 |

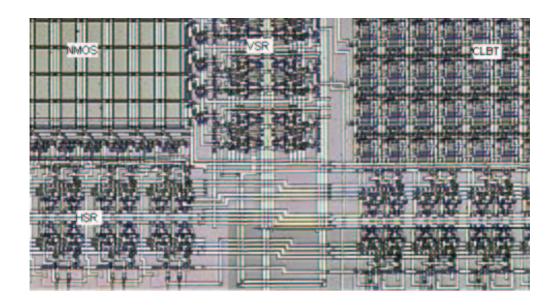

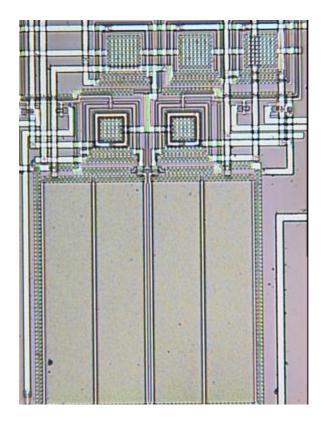

| 5.2  | The photomicrograph of the test arrays of the second batch.                     |

|------|---------------------------------------------------------------------------------|

|      | HSR and VSR are the horizontal and vertical shift registers                     |

|      | respectively                                                                    |

| 5.3  | Simplified nMOSFET test structure layout with $4 \times 4$ DUTs                 |

|      | (left) and $n \text{MOSFET}$ test structure proposed by L. Portmann [PLK98]. 58 |

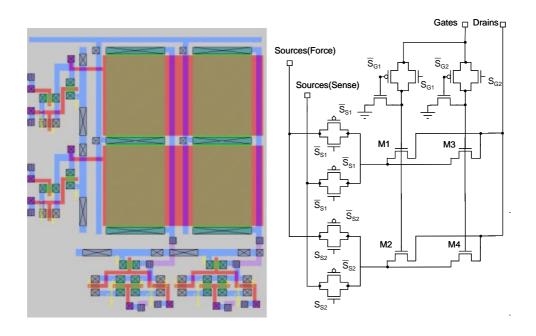

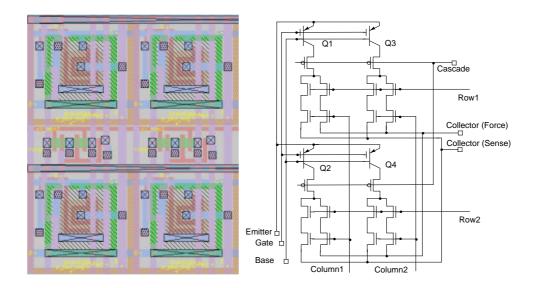

| 5.4  | The original CLBT test array circuit with $4 \times 4$ DUTs 60                  |

| 5.5  | The modified CLBT test structure layout with $4 \times 4$ DUTs (left)           |

|      | and schematic diagram of the new test structure (right) 61                      |

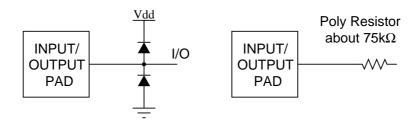

| 5.6  | A typical analog I/O pad (left) and I/O pad for CLBT gate                       |

|      | (right)                                                                         |

| 5.7  | Schematic diagram of a shift register bit                                       |

| 5.8  | Photograph of the experimental setup                                            |

| 5.9  | Setup for automatically extracting the matching properties of                   |

|      | cascoded CLBTs (top left), CLBTs operating as $p$ MOSFETs                       |

|      | (top right) and $n$ MOSFETs (bottom) 66                                         |

| 5.10 | Matching properties of $n$ MOSFET under $100nA$ current level                   |

|      | in $Chip1$ . The top figure shows the current values (in $A$ ) in one           |

|      | dimensional view and the bottom one shows the values in two                     |

|      | dimensional view                                                                |

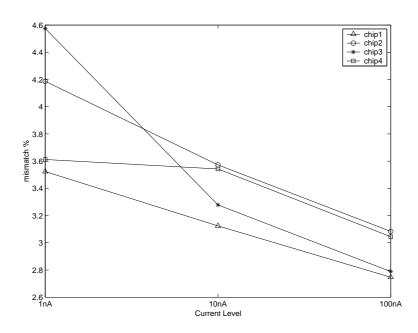

| 5.11 | Mismatch of the $n$ MOSFETs at different current levels 70                      |

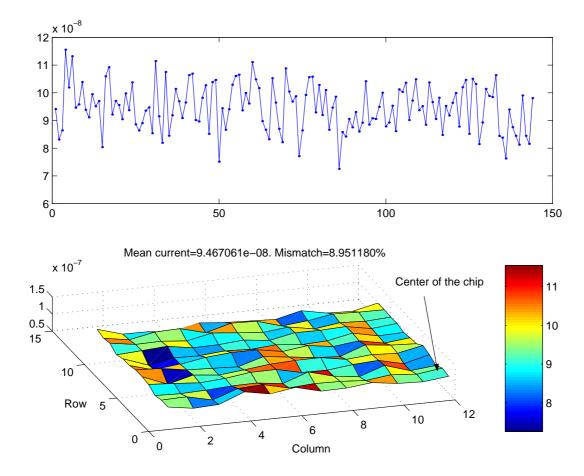

| 5.12 | Matching properties of $pnp$ CLBTs under $100nA$ current level                  |

|      | in $Chip1$ . The top figure shows the current values (in $A$ ) in one           |

|      | dimensional view and the bottom one shows the values in two                     |

|      | dimensional view                                                                |

| 5.13 | Mismatch of the CLBTs at different current levels 72                            |

| 5.14 | Matching properties of CLBTs operating as $p$ MOSFETs under                     |

|      | 100nA current level in $Chip1$ . The top figure shows the current               |

|      | values (in $A$ ) in one dimensional view and the bottom one shows               |

|      | the values in two dimensional view                                              |

| 5.15 | Mismatch of the $p$ MOSFETs at different current levels             | 74 |

|------|---------------------------------------------------------------------|----|

| 5.16 | The estimated mismatch of the scaled $p$ MOSFETs at different       |    |

|      | current levels                                                      | 75 |

| 5.17 | The mismatches of the transistor pairs at different current levels. | 78 |

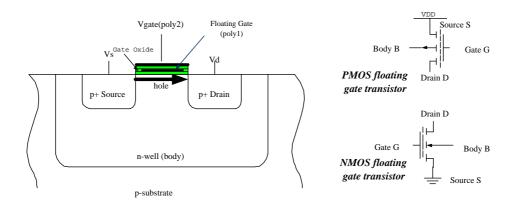

| A.1  | Cross-sectional view of PMOS floating gate transistor (left) and    |    |

|      | the symbols of NMOS and PMOS floating gate transistors (right).     | 83 |

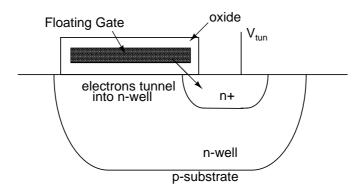

| A.2  | Cross-sectional view showing how an $n$ -well is used to remove     |    |

|      | electron from floating gate through tunnelling                      | 84 |

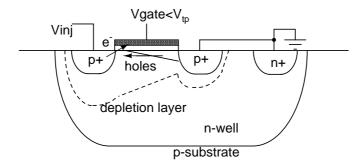

| A.3  | Cross-sectional view showing how hot electron injection is achieved |    |

|      | in a $p$ MOSFET                                                     | 86 |

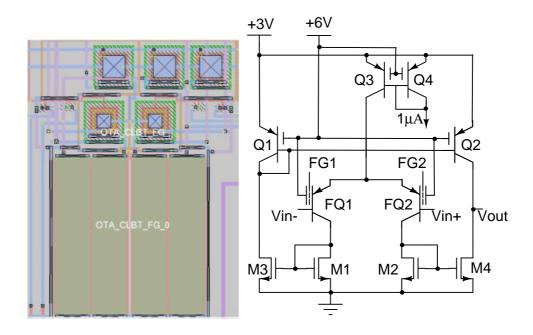

| B.1  | Layout of FGOTA (left, current source $Q4$ not shown) and its       |    |

|      | schematic diagram (right)                                           | 88 |

| B.2  | Photomicrograph of the FGOTA                                        | 89 |

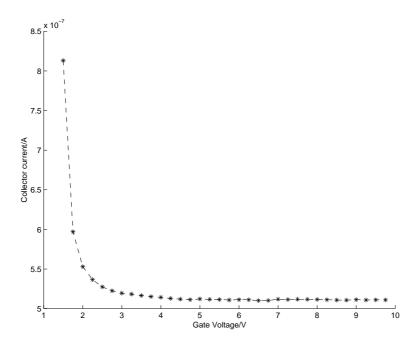

| В.3  | Residual gate effects of a pnp CLBT                                 | 90 |

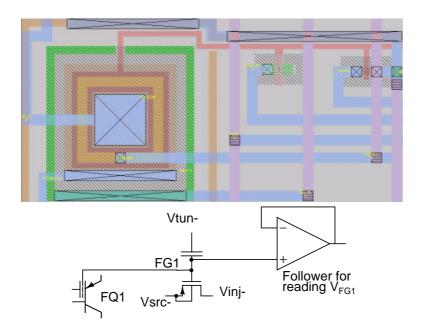

| B.4  | Layout of FG-CLBT (top left), the tunnelling n-well (top mid-       |    |

|      | dle), and injection $p$ MOSFET (right top) and the schematic        |    |

|      | diagram (bottom).                                                   | 92 |

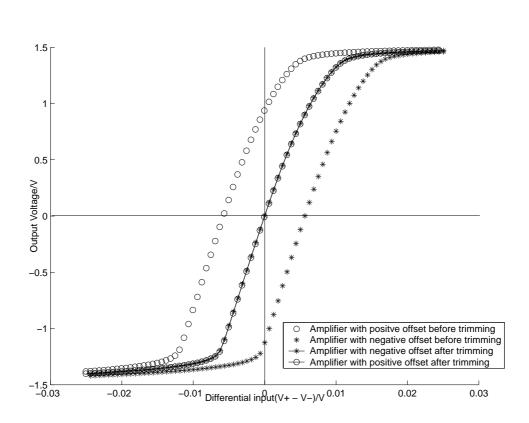

| B.5  | VTCs of trimmed and untrimmed OTA (all the measurements             |    |

|      | were taking $1.5V$ as reference)                                    | 95 |

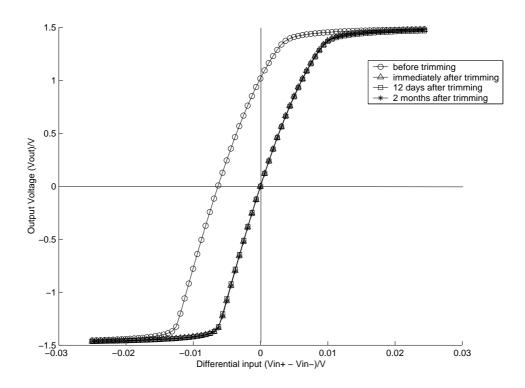

| B.6  | VTCs of trimmed and untrimmed FGOTA (all the measure-               |    |

|      | ments were taking $1.5V$ as reference)                              | 96 |

# List of Tables

| 3.1 | Previous results comparing the matching properties of MOS-                  |    |

|-----|-----------------------------------------------------------------------------|----|

|     | FETs and CLBTs                                                              | 29 |

| 4.1 | The areas of different structures of CLBTs ( $\lambda^2$ ). In this thesis, |    |

|     | $\lambda=0.8\mu m$ was used. Bare CLBT refers to CLBT not cascoded.         | 44 |

| 4.2 | Characteristics of CLBTs of different sizes                                 | 50 |

| 5.1 | Voltages applied to the base and gate of CLBTs and MOSFETs                  |    |

|     | for different current levels                                                | 67 |

| 5.2 | Average mismatch of $n$ MOSFETs (%)                                         | 70 |

| 5.3 | Average mismatch of CLBTs (%)                                               | 72 |

| 5.4 | Average mismatch of $p$ MOSFET (%)                                          | 74 |

| 5.5 | Mismatch of the scaled $p$ MOSFET estimated using the Law of                |    |

|     | Area (%)                                                                    | 75 |

| 5.6 | The mismatches of the transistor pairs at different current levels          |    |

|     | (%)                                                                         | 78 |

# Chapter 1

# Introduction

# 1.1 Motivation and Objectives

The two main types of transistors used in today's Integrated Circuits (ICs) are the Bipolar Junction Transistor (BJT) and the Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET), or simply MOS transistor. Complementary MOS (CMOS) is the process and circuit technique of using two types of complementary MOSFETs, namely pMOSFETs and nMOSFETs, which has the advantage of high speed and low power dissipation. With the advent of IC technology, digital circuits have become widespread and the CMOS process has been optimized for digital applications [IF94]. In spite of this, BJTs still retain many advantages over those of CMOS for some critical analog applications such as bandgap voltage references [DLVO85], photodetectors [ZCFK98], silicon cochlea [vSFV96], temperature sensors [BH96], and Digital-to-Analog Converters (DACs) [BBW90]. However, since CMOS and bipolar processes are incompatible, additional masking steps are required to combine both types of transistors on the same chip, which is the more expensive BiCMOS process. As System-on-a-Chip (SOC) becomes increasingly popular, the need for integrating the analog peripherals and digital processing cores on the same chip is increasing [Chi98]. Under such a situation, the Compatible Lateral Bipolar Transistors (CLBTs) have received renewed interest.

Figure 1.1: Cross-sectional view of CLBT.

CLBTs are the parasitic BJTs formed in CMOS process by operating the MOSFETs in bipolar mode (explained in detail in Section 4.2). The structure is shown in Figure 1.1. Therefore, BJTs and MOSFETs can be realized on the same wafer without additional costs using a standard CMOS process. MOSFETs can be used for implementing high density digital logic while the CLBTs can be used in the analog parts.

Technology downward scaling continues to be a major trend in the IC industry. According to the projections of the Semiconductor Industry Association (SIA), the feature size of the IC process would reach  $0.05\mu m$  by the year 2011 [Josed]. Deep submicron technology requires further lowering of the supply voltage; on one hand to prevent the increase in electric field when device dimensions are decreasing with constant supply voltage, and, on the other hand, to reduce power consumption since the number of transistor per unit area is increasing in quadratic manner. In fact, the supply voltage and power per chip are predicted to be 0.5V and 174W by 2011 respectively by SIA. Analog circuits operating under ultra-low power supply voltages require well-matched devices for proper operation. Matching properties refer to the similarities between the electrical properties of two identically designed and used components after fabrication. However, MOSFETs fail to meet such requirements especially in low current level operations. Since CLBTs have been shown to

have better matching properties than CMOS [Vit83, PA89, vSFV96, RHL97], a study of low voltage and low power circuits incorporating CLBTs becomes more meaningful.

CLBTs have been gaining interest since 1969 [LHIK69]. CLBTs were analyzed and incorporated in current mirrors and amplifiers, and were shown to have lower noise than those incorporating only MOSFETs by Vittoz in 1983 [Vit83]. In 1985, accurate CMOS voltage references incorporating CLBTs were realized [DLVO85]. Arreguit then proposed a more complete model for CLBTs in 1989 in his PhD thesis [Arr89] and the CLBT was shown to have better matching properties than MOSFETs since they push the flow of carriers away from the surface of the device. The matching of CLBT current mirrors also has been shown to be better than that of MOSFET current mirrors, especially under low current levels [PA89]. Applications have used CLBTs for their improved matching properties over MOSFETs, some examples being a Variable Gain Control (VGC) circuit [PA89], a silicon cochlea [vSFV96], and a logarithmic photoreceptor [RHL97].

Even though many applications of CLBTs appear in the literature, to the best of our knowledge, the matching properties of CLBTs have not been investigated systematically and quantitatively hitherto. Matching properties, however, are very critical in the design of low power analog circuits. The main aim of this thesis is to study the matching properties of CLBTs and compare them with nMOSFETs and pMOSFETs fabricated with a standard CMOS process in a systematic and quantitative fashion. Applications of CLBTs for improved circuits were also studied.

## 1.2 Contributions

Test chips containing arrays of cascoded pnp CLBTs with p-type guard rings and nMOSFETs were fabricated using the standard AMI-ABN 1.5 $\mu m$  n-well

process. An efficient parameter extraction array for bipolar devices was designed. This design provides a good balance between the number of devices to be tested, number of pins and accuracy.

The pnp CLBTs and nMOSFETs were designed to have similar layout areas. There were in total 900 nMOSFETs and 576 pnp CLBTs. A testing setup was developed to perform automatic extraction of transistor parameters. Using this setup, the matching properties of the pnp CLBTs and nMOSFETs, as well as the pnp CLBTs operating as pMOSFETs, were measured.

A preliminary study of the application of Floating-Gate CLBTs (FG-CLBTs) was also carried out. An Operational Transconductance Amplifier (OTA) incorporating FG-CLBTs as the input differential pair was designed and fabricated. The advantage of using CLBTs in OTAs is that they are expected to have lower noise. By utilizing the residual gate effects of the CLBTs, we showed that it was possible to trim the offset of the OTA by using hot electron injection and electron tunnelling in this standard  $1.5\mu m$  process.

# 1.3 Organization of the Thesis

An introduction on the structures and representative fabrication technologies of CMOS, BJT, and BiCMOS circuits is presented in Chapter 2. In Chapter 3, matching properties are introduced. In Chapter 4, the structures, modeling, and main characteristics of CLBTs are discussed. Experimental results of the DC characteristics of the CLBTs and MOSFETs fabricated using this process are also included in this chapter. Experimental results of the matching properties of CLBTs, nMOSFETs and pMOSFETs and the comparisons and analysis are given in Chapter 5. Conclusions are given in Chapter 6. Finally, a review of floating gate technologies is presented in Appendix A and the design, characteristics and experimental results of the trimmable FGOTA are given in Appendix B. Process parameters are given in Appendixes C and D.

# Chapter 2

# Devices and Fabrication

# **Processes**

## 2.1 Introduction

Since the invention of planar technology in the 1960's, the integration of large numbers of devices on a single silicon die became possible and effective. Bipolar, CMOS and BiCMOS Integrated Circuit (IC) processes were then developed in the 60's, 70's, and 80's respectively. This chapter presents the structures and models of the Bipolar Junction Transistors (BJTs) and Metal-Oxide-Semiconductor Field Effect Transistors (MOSFETs), which are the representative active elements in bipolar and CMOS processes respectively. Representative IC processes and the pros and cons of these technologies and devices are also discussed. All these serve as the basis for the understanding of the following chapters.

## 2.2 BJTs

#### 2.2.1 Structure and Modeling of BJTs

There are three terminals in a bipolar transistor, namely the collector C, base B, and emitter E (Figure 2.1). Bipolar technology is usually optimized for vertical npn BJTs [Arr89, GM93] and Figure 2.1 shows the cross-sectional view of a vertical npn transistor. For an npn transistor in the forward active mode, the base-emitter junction would be forward biased with  $V_{BE} > 0$  and the base-collector junction would be reverse biased ( $V_{BC} < 0$ ). The electrons are injected into the base as minority carriers and collected in the collector. The collector current  $I_C$ , base current  $I_B$ , and forward current gain  $\beta_F$  can be expressed as [GM93]:

$$I_C = qAD_n \frac{n_{po}}{W_B} \exp \frac{V_{BE}}{U_T} \tag{2.1}$$

$$I_B = \left(\frac{1}{2} \frac{n_{po} W_B q A}{\tau_b} + \frac{q A D_p}{L_p} \frac{n_i^2}{N_D}\right) \exp \frac{V_{BE}}{U_T}$$

(2.2)

$$\beta_F = \frac{I_C}{I_B} = \frac{1}{\frac{W_B^2}{2\tau_b D_n} + \frac{D_p}{D_n} \frac{W_B}{V_D} \frac{N_A}{N_D}}$$

(2.3)

where q is the electronic charge  $(1.6 \times 10^{-19}C)$ , A is the effective emitter area,  $D_n$  is the electron diffusion constant,  $W_B$  is the effective base width,  $n_{p0}$  is the equilibrium electron concentration in the base,  $U_T$  is the thermal voltage,  $\tau_b$  is the minority-carrier lifetime in the base,  $D_p$  is the diffusion constant for hole,  $L_p$  is the diffusion length for hole in emitter,  $n_i$  is the intrinsic carrier concentration in silicon,  $N_A$  is the acceptor concentration, and  $N_D$  is the donor concentration.

From the equations, the collector current depends on both process parameters and layout design. IC designers can only control  $I_C$  through the layout of different emitter areas and the emitter area is defined as the horizontal area of the base and emitter interface (Equation 2.1).

Figure 2.1: Cross-sectional view of vertical npn bipolar transistor (left) and npn and pnp bipolar transistor symbols (right).

#### 2.2.2 Standard BJT Process and BJT Characteristics

Standard bipolar integrated circuits using the bipolar process optimized for vertical npn BJT are usually fabricated on a lightly doped (111)-oriented p-type substrate (Figure 2.1) [Has01]. (111) silicon crystal helps to prevent the formation of the parasitic pMOSFETs between the base and the isolations. Then an  $n^+$ -buried layer is formed, followed by the growth of an n-type epitaxial layer. Isolation diffusion, base implant and emitter diffusion then follow to form the isolations, base, and emitter and collector regions respectively. Other active and passive devices are formed based on these masks. The optimization of the vertical npn BJTs poses limitation of the performance on pnp BJTs and in fact, only lateral and substrate pnp BJTs can be formed in such a process.

The characteristics of bipolar processes optimized for vertical npn transistors are summarized as follows [Arr89]:

• A  $n^+$  buried layer is implemented to prevent undesirable injection of carriers into the p-substrate and to decrease the collector series resistance (Figure 2.1).

- The base width, the vertical distance between the  $n^+$  emitter region and the n epitaxial collector region, is minimized to increase  $\beta_F$  (Equation 2.3).

- The emitter region is heavily doped to increase the ratio of emitter to base doping densities  $N_D/N_A$  to increase  $\beta_F$  (Equation 2.3).

- Early effect and avalanche multiplication effects are minimized by keeping the collector doping as low as possible. The Early effect refers to the fact that the depletion width of base-collector junction will increase as  $V_{CB}$  increases, thus lowering the effective base width. According to Equation 2.1,  $I_C$  will increase even under constant  $V_{BE}$ , thereby lowering the output resistance.

Since most bipolar processes are optimized for vertical npn transistors, they have higher gain (100 to 200) than that of substrate (60 to 100) and lateral (30 to 50) pnp transistors [Arr89]. Compared with MOSFETs, bipolar junction transistors (BJTs) have more driving power to overcome the speed bottleneck of driving large capacitive loads. However, they consume more power than MOSFETs, so they are suitable for high speed but low transistor density design.

# 2.3 MOSFETs and Complementary MOS (CMOS)

# 2.3.1 Structure and Modeling of MOSFETs

The polysilicon-gate CMOS process is optimized to form complementary pMOS-FET and nMOSFET transistors on a common substrate. nMOSFETs and pMOSFETs use electrons and holes as majority carriers respectively. Unlike bipolar devices, they only use either holes or electrons as carriers, so, they are also known as unipolar devices. Figure 2.2 shows the cross-sectional view

Figure 2.2: Cross-sectional view of an nMOSFET (left) and the symbols for nMOSFET and pMOSFET transistors (right).

of an nMOSFET and its symbol respectively. There are four terminals in an nMOSFET, namely the source S, gate G, drain D, and body B. The gate is isolated from the well by a layer of thin gate oxide. The body refers to the well and is usually grounded to the lowest potential of the circuit in operation. During normal operations, the drain is connected to a higher potential with respect to the source and body such that  $V_{DS} > 0V$  and  $V_{SB} = 0V$ . As a result, the n-type drain, p-type well, and n-type source form a pair of back-to-back diodes and would only conduct a small leakage current which is known as subthreshold conduction or weak inversion and obeys an exponential law. If the gate-source voltage  $V_{GS}$  is larger than a certain voltage, namely the threshold voltage  $V_T$ , electrons would accumulate on the surface near to gate oxide to an extent such that the electron concentration is higher than the hole concentration. An n-type region is then effectively formed on the surface and this phenomenon is called strong inversion and the channel is called the inversion layer. The nMOSFET would then be able to conduct drain current  $I_D$ , which depends on both  $V_{GS}$  and  $V_{DS}$ . The nMOSFET is said to be in linear mode. When  $V_{DS} > V_{GS} - V_T$ ,  $I_D$  will no longer depend on  $V_{DS}$  and the nMOSFET is in saturation mode. The I-V transfer characteristic of nMOSFET can be expressed as [EKV95]:

Weak inversion  $(V_S > V_P \text{ and } V_D > V_P)$ :

$$I_D = 2n\beta U_T^2 \exp\frac{V_P}{U_T} \left(\exp\frac{-V_S}{U_T} - \exp\frac{-V_D}{U_T}\right)$$

(2.4)

Linear mode under strong inversion  $(V_S \leq V_P \text{ and } V_D \leq V_P)$ :

$$I_D = n\beta(V_P - \frac{V_S + V_D}{2})(V_D - V_S)$$

(2.5)

Saturation mode under strong inversion  $(V_S \leq V_P \text{ and } V_D > V_P)$ :

$$I_D = \frac{n\beta}{2}(V_P - V_S)^2 \tag{2.6}$$

where

$$V_P \cong \frac{V_G - V_{T0}}{n} \tag{2.7}$$

$$\beta = \frac{W}{L} \mu_n C_{ox} \tag{2.8}$$

$$V_{T0} = V_{FB} + \Psi_0 + \gamma \sqrt{\Psi_0}$$

(2.9)

and  $V_P$  is the pinch-off voltage,  $V_{T0}$  is the threshold voltage when the channel is in equilibrium and depends on the surface charge density, n is the slope factor,  $\beta$  is the current factor,  $U_T$  is the thermal voltage, W and L are the width and length of the gate respectively,  $\mu_n$  is the mobility of electron,  $C_{ox}$ is the gate oxide capacitance per unit area,  $V_{FB}$  is flat band voltage,  $\Psi_0 =$  $2\Phi_F + several\ U_T$  where  $\Phi_F$  is the Fermi potential, and  $\gamma$  is the body factor. Note that both  $V_{T0}$  and  $\gamma$  also depend on  $C_{ox}$  and the doping of the bulk.

pMOSFETs have a similar structure to nMOSFETs. The majority carriers of pMOSFETs are holes. The source and drain regions of a pMOSFET are p-type while the body is of n-type. It is possible to put nMOSFETs and pMOSFET on the same chip without adding many process steps, and this is called CMOS technology.

# 2.3.2 Standard *n*-well CMOS Process and MOSFETs Characteristics

There are three kinds of CMOS processes, n-well, p-well and twin-well. In Figure 2.3, the substrate is of p-type, so an nMOSFET can be formed directly on it. In order to form a pMOSFET, an n-type well has to be formed first as the body of the pMOSFET. Then, the source and drain of the pMOSFET are formed by creating p-type regions in the n-well. This is known as an n-well CMOS process. It is also possible to have a p-well process with nMOSFETs being built in the p-wells and pMOSFETs built directly on an n-substrate (shown in Figure 2.2). In some processes, which are called the twin-well processes, both the p-well and n-well are formed simultaneously. Twin-well processes are usually found in deep submicron processes because in these processes, the bodies of the MOSFETs have to be highly doped to reduce the chance of punchthrough. Counter doping becomes very unfavorable and highly doped n-wells and p-wells have to form separately. However, it should be noted that in a twin-well process, either one type of wells are still connected together to the substrate as the substrate must be either p or n-type. In this thesis, an n-well process was used and so, only the n-well processes will be discussed.

For an n-well process, CMOS integrated circuits are usually fabricated on (100)-oriented p-type substrate, which is heavily doped with boron to minimize the resistivity. The (100) silicon creates lower surface state density and improves the threshold voltage control [Has01]. An epitaxial layer of about 5 to  $10\mu m$  is then grown followed by n-well diffusion. A moat mask is then used to define the active areas where the MOSFETs will form. After the formation of gate oxide, threshold adjust implantation is used to adjust the threshold voltage of the MOSFETs to the range of 0.7V to 0.9V. Polysilicon deposition and patterning and source/drain implantation then follow. The following can be observed for an n-well CMOS process:

Figure 2.3: Cross-sectional view of an *n*-well CMOS process with latch-up circuit identified (left) and the extracted model of the latch-up circuit (right) (adapted from [KL99]).

Firstly, the n-well has higher dopant concentration due to counter doping, so pMOSFETs have poorer parameters than nMOSFETs because the carrier mobility in pMOSFETs degrades due to the counter doping [Has01, LHC86].

Secondly, as shown in Figure 2.3, it is possible for the nMOSFETs and pMOSFETs to form an unfavorable latch up circuit. Latch-up is defined as the generation of a low-impedance path in CMOS chips between the power supply rail and the ground rail due to interaction of parasitic pnp and npn transistors. Under normal conditions, there is only a high impedance path between the power rails as Q1 and Q2 are off. As shown in the model of latch up circuits, if there is an increase in the collector current of either parasitic bipolar transistors due to an external disturbance, the transistors will drive each other in positive feedback path. In the worst case, it would destroy the device by forming a too large current [KL99]. To prevent latch up, either the  $R_{well}$  or  $R_{sub}$  has to be reduced, which could be achieved by increasing the doping level of the well or adding a guard ring to trap the injected minorities, or the gain of the bipolar transistors has to be reduced by increasing the separation distance between opposite type MOSFETs. Usually, the minimal distance between opposite types of MOSFET specified by the design rule of

a process is enough to prevent latch-up in a properly-biased digital circuit. However, when the wells are biased differently as in Compatible Lateral Bipolar Transistors (CLBTs), guard rings have to be added (detailed in Section 4.8).

Thirdly, unlike the bipolar processes, CMOS processes do not require a buried layer as MOSFETs are surface devices, in which the carriers flow near to the  $Si-SiO_2$  interface. However, when the MOSFETs are operated as lateral bipolar devices, considerable minorities injected from the source or drain into the body will travel vertically and be collected by the substrate in the absence of buried layers. The lateral gain will then be significantly decreased.

# 2.4 BiCMOS Technology

CMOS is currently the major technology used in integrated circuit designs. CMOS devices feature high input impedance, low offset switches, high packing density, low switching power consumption, and high scalability. Despite these advantages, CMOS still cannot completely replace bipolar devices not just in analog circuits but also the digital ones since bipolar devices retain some advantages over CMOS, among which are larger capability to drive capacitive loads, larger transconductance, lower 1/f noise, and better matching properties. BiCMOS technologies combine CMOS and bipolar technologies on the same chip so the advantages of both types of transistors can be used together. Then, the low-noise high speed parts could be achieved by bipolar circuits and the low-speed logic parts could be implemented with CMOS. Usually, a typical mixed-signal circuit contains 90-95% digital circuits and 5-10% analog circuits [Has01].

However, the BiCMOS process cannot just be a simple modification of BJT or CMOS process. Analog BiCMOS processes require at least fifteen masks (in contrast to the baseline of eight masks in BJT and nine masks in CMOS), which is much more complicated. Additional processing steps such as buried

layers, deep n+ sinkers, and base diffusions must be included in addition to the CMOS processes. Such complicated process means also higher wafer costs, longer manufacturing time, lower process yields, more difficult controls on the diffusions, and most importantly, more expensive products. Therefore, the inexpensive CLBTs in CMOS provide an attractive alternative to using BiCMOS.

# 2.5 Summary

In this chapter, modern IC technologies, namely the bipolar, CMOS and BiC-MOS processes have been presented. The most commonly used devices, BJTs and MOSFETs were discussed in details, and their structures and modeling were presented.

# Chapter 3

# **Matching Properties**

## 3.1 Introduction

In this chapter, the background of matching properties of MOSFETs and BJTs is presented. The importance and equations of mismatch measurements are discussed. Previous work on the matching properties of MOSFETs and BJTs is summarized. This chapter provides a basis for the discussion of the matching properties of CLBTs.

# 3.2 Importance of Matched Devices in IC Design

# 3.2.1 What is Matching?

Matching deals with statistical device differences between pairs of identically designed and identically used active or passive elements such as transistors, resistors, and capacitors [PTV98]. Devices specifically constructed to obtain a known constant ratio are called *matched devices* [Has01]. Mismatch is the process that causes time-independent random variations in physical quantities of such devices. Analog circuits place particularly stringent requirements on

matching resistors, capacitors, and transistors because the vital circuit components, such as operational amplifiers, Digital-to-Analog Converters (DACs), multiplexed analog systems, and reference sources demand highly matched current mirrors and differential pairs for high enough accuracy [Gre92]. Additionally, the trends described in the following subsections make the study of better matching devices become even more important.

## 3.2.2 Low-power Systems

Matched components are becoming increasingly important since low-voltage circuits have become a major trend and will surely dominate the electronic industry in the future. In digital circuits, the supply voltage is expected to reach 0.5V (minimum logic Vdd) by the year of 2011 [Josed]. Firstly, there are more needs for portable systems such as low-power hearing aids, cardiac pacemakers, cellular phones, pagers, portable computers and telecommunications products. Moreover, as transistor density and operating frequency increase, heat dissipation becomes a more urgent problem to be solved, which requires the further lowering of supply voltage. As System-On-a-Chip (SOC) becomes an effective means for realizing cost-effective products and more efficient electronic systems, analog circuits will be restricted to operating under such low power supplies. When the voltage supply decreases, it becomes more difficult to keep the signal-to-offset, or signal-to-noise ratio large enough for accurate operation [IF94]. Analog circuits which work well under conventional voltage supplies may malfunction under low voltage supplies due to the increase in the significance of the mismatch.

# 3.2.3 Device Size Downward Scaling

The impact of matching also increases as the dimensions of the devices are being reduced. As predicted by the Semiconductor Industry Association (SIA),

the feature size of semiconductor devices would reach 50nm in 2011 [Josed]. As a result, the mismatching caused by the limited resolution precision of lithographical process during IC fabrication would become more explicit as the relative error increases.

#### 3.2.4 Analog Circuits and Analog Computing

Even though it has been predicted for years that analog circuits would fade out very soon, there are still strong needs for analog circuits in today's IC industry. For example, Analog-to-Digital Converters (ADCs) and Digital-to-Analog Converters (DACs) are necessary for electronic equipment to interact with the analog physical world. High performance anti-aliasing filters and reconstruction filters are required to implement high speed front ends in communication systems [JM97]. In these circuits, the associated current mirrors and differential pairs should have very good matching properties.

At the same time, there has been an increase in interest in analog computing and neuromorphic engineering in recent years. Neuromorphic Engineering is a field based on the design and fabrication of artificial neural systems, such as vision systems, head-eye systems, and roving robots, whose architecture and design principles are based on those of biological nervous systems [Mea89]. In these two areas, both active and passive elements operate in analog circuits for precise computation. For example, translinear circuits use MOSFETs operating in the subthreshold region for multiplication and logarithmic operations [Min99]. Well matched devices are thus required to realize such systems and the design of precise analog circuits requires a thorough understanding of the matching behavior of components available in any given technology.

## 3.3 Measurement of Mismatch

Due to the importance of matching properties, extensive studies have been carried out on the matching properties of capacitors [STK84, McC81], MOSFETs [LHC86, PTV98, PDW89, WPM97, HHG98, BSR<sup>+</sup>95, LWMM98] and bipolar transistors [CE96a, TI96]. Significant results have been achieved, especially for MOSFETs. The followings summarize some of the related theories of matching properties and the important results of the matching properties of MOSFETs and bipolar transistors.

#### 3.3.1 Definitions and Statistics of Mismatch

#### Two commonly used equation sets

There are different definitions of mismatch in literature [Has01, Gre92, PGJ<sup>+</sup>95]. In [Has01], the mismatch  $\delta$  between two devices is usually expressed as a deviation of the measured device ratio from the intended device ratio and is expressed by the following equation:

$$\delta = \frac{\frac{x_2}{x_1} - \frac{X_2}{X_1}}{\frac{X_2}{X_1}} \tag{3.1}$$

where the intended values are  $X_1$  and  $X_2$  and the measured values are  $x_1$  and  $x_2$  [Has01]. For N samples, the mean of the mismatch  $m_{\delta}$  is defined as:

$$m_{\delta} = \frac{1}{N} \sum_{i=1}^{N} \delta_i \tag{3.2}$$

and the standard deviation of the mismatches  $\sigma_{\delta}$  is defined as:

$$\sigma_{\delta} = \sqrt{\frac{1}{N-1} \sum_{i=1}^{N} (\delta_i - m_{\delta})^2}$$

(3.3)

Another statistical approach for evaluating the stochastic mismatch between two identically designed elements on the same chip was proposed by Pergoot in 1995 [PGJ<sup>+</sup>95]. The mismatch between two identical parameters

P1 and P2, measured on two different identically designed elements, is defined as the standard deviation of the normal distribution of N (N > 30) absolute differences  $\delta_a = \Delta P = (P1 - P2)$  (e.g. for threshold voltage) or relative differences  $\delta_r = \Delta P/P = (P1 - P2)/(P1 + P2) * 200[\%]$  (e.g. for transconductance or resistance). The mismatch is thus defined in either of the following forms,

$$\sigma(\Delta P) = \sqrt{\frac{1}{N-1} \sum_{i=1}^{N} (\delta_a - m_{\delta a})^2}$$

(3.4)

$$\sigma(\Delta P/P) = \sqrt{\frac{1}{N-1} \sum_{i=1}^{N} (\delta_r - m_{\delta r})^2}$$

(3.5)

where  $m_{\delta a}$  and  $m_{\delta r}$  are the means of  $\delta_a$  and  $\delta_r$  respectively.

#### Formulae used in this thesis

There are two main differences between the above two methods. Firstly, in [Has01], the ratio between the two parameters is emphasized and the intended ratio has to be known while the one in [PGJ<sup>+</sup>95] requires only the measured values. The first one is especially useful for measuring the mismatch of devices having ratio other than 1:1, while the second one is simpler and no absolute intended parameter value is required and only the mean of the measured parameters is used for computation ((P1 + P2)/2). Secondly, the first method defined the mismatch as the relative ratios and the second one defined it as the standard deviation of the relative ratios. However, this is not of great importance.

In this thesis, the mismatches of currents in CLBTs and MOSFETs in the arrays will be measured first. Then the adjacent transistors would be paired up as current mirror and their mismatch will be measured. When measuring the mismatch of currents in the MOSFET and CLBT array, the relative differences of the second method are used. Since arrays of independent transistors are used instead of transistor pairs, the mean of the measured current  $\bar{I}$  will be used as

the reference. The equation for the mismatch of the measured currents  $\sigma_{\delta_I}$  of N transistors is shown as follows:

$$\sigma_{\delta_I} = \sqrt{\frac{1}{N-1} \sum_{i=1}^{N} (\delta_{Ii} - m_{\delta_I})^2}$$

(3.6)

where,

$$\delta_{I_i} = \frac{I_i - \bar{I}}{\bar{I}} \tag{3.7}$$

$$m_{\delta_I} = \frac{1}{N} \sum_{i=1}^{N} \delta_{Ii} \tag{3.8}$$

and  $I_i$  is the measured current of the *ith* transistor.

In this work, Equations 3.1 to 3.3 will be used to calculate the mismatch of the transistor pairs.

#### 3.3.2 Types of Mismatches

In general, there are two sources of parameter variations in integrated circuit fabrication processes.

- a. Systematic mismatches [STK84, Elz96] These types of mismatches would affect adjacent elements with identical geometries similarly. The main causes include [Has01]:

- Process Biases This refers to geometry shrinking or expanding during photolithography, etching, diffusion, and implantation. The process bias is the difference between the drawn width and the actual width of components.

- 2. Variations in Etch Rate This refers to the variations in etch rate of oxide by the etchant in different sizes of openings. Since large openings grant more access to the etchant, the etch rate is faster.

- 3. Stress Gradients Silicon is piezoresistive, which means that its resistivity will change under different stresses. Due to the tension

produced by the packaging, there is always a gradient of stress, and thus a change of resistivity across the die.

4. Temperature Gradients - According to Equation 2.1, the collector current depends exponentially on the temperature of the device. This is also true for MOSFETs in subthreshold region (Equation 2.4). This temperature effect becomes extremely important when power transistors are built on the same chip as matched devices. The best way to reduce the temperature effect is to put the matched devices in isotherms and far away from the power transistors.

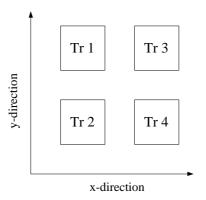

Systematic mismatch will become more serious when the transistors are unequally designed or asymmetrically placed. On the other hand, it can be reduced by proper layout techniques. For example, variations in sheet resistance and junction depth of the implanted and diffused regions across the wafer resulting from non-uniform conditions during the predeposition and diffusion of the impurities could be corrected by using a common-centroid geometry (Figure 3.1).

Figure 3.1: Common-centroid layout constructed with 4 unit devices connected as QUAD. Transistor T1=Tr1+Tr4, transistor T2=Tr2+Tr3.

b. Random (Stochastic) mismatches [STK84, Elz96] Such mismatches are caused by random statistical fluctuations and irregularities of the components [Has01]. For example, the edges of the polysilicon exhibit microscopic irregularities, which resulted from the granularity of the polysilicon and imperfections in the photoresist. As a result, the resistors and capacitors, as well as transistors, formed by the polysilicons will vary through the chip. This type of mismatch differs from element to element, and cannot be corrected by layout techniques. They are normally distributed with a mean of zero. Therefore, the only way to reduce the mismatch is to improve the fabrication process and increase the components areas. Random mismatches pose the ultimate limitation on the achievable accuracy for circuit designers.

There are two kinds of fluctuations in this kind of mismatch, peripheral fluctuations (fluctuations that occur only along the edges of the device) and area fluctuations (fluctuations occur throughout the device). When the area to edge length ratio is large enough, the area fluctuations will dominate and the peripheral effects can be neglected. For example, the mismatch of a capacitor with capacitance C can be represented as [Has01]:

$$\sigma_{\delta_C} = \frac{1}{\sqrt{C}} \sqrt{k_a + \frac{k_p}{\sqrt{C}}} \tag{3.9}$$

where  $k_a$  and  $k_p$  are constants representing the contribution of area fluctuations and peripheral fluctuations respectively. When the area is large enough (with large C), the term containing  $k_p$  can be neglected and the mismatch of the capacitors depends only on the area fluctuation.

#### 3.3.3 Matching Properties of MOSFETs

There have been three main types of studies on the matching properties of MOSFETs. Only the first two are of interest in this thesis:

#### a. Main mismatch sources and matching modeling

Referring to the MOSFET current equations (Equation 2.4 to 2.9), the mismatch of drain current can depend on the threshold voltage  $V_T$ , body factor  $\gamma$  and current factor  $\beta$  [PDW89]. However, due to the difficulty in controlling the diffusion process, surface charge formation and oxide thickness, the main source of error is the threshold voltage and the current factor. The mismatch of drain current can thus be represented in terms of the mismatches of  $V_T$  and  $\beta$ . Generally, MOSFETs operate in the saturation region in analog circuits. In the saturation region, the mismatches of the drain interconnect paths would make no significant contribution to the current mismatch [LHC86, BGS96]. In this thesis, we only consider the mismatch model for MOSFETs in the saturation region.

In saturation, the variances of the threshold voltage  $\sigma_{V_T}^2$  and the current factor  $\sigma_{\beta}^2$  [BSR<sup>+</sup>95, LWMM98, PDW89, LHC86] are represented as:

$$\sigma^{2}(\Delta V_{T}) = \frac{A_{1VT}^{2}}{W_{eff}L_{eff}} + \frac{A_{2VT}^{2}}{W_{eff}L_{eff}^{2}} - \frac{A_{3VT}^{2}}{W_{eff}^{2}L_{eff}}$$

(3.10)

$$\frac{\sigma^2(\Delta\beta)}{\beta^2} = \frac{A_{\beta^2}^2}{W_{eff}L_{eff}} + \frac{A_{L^2}^2}{W_{eff}L_{eff}^2} + \frac{A_{W^2}^2}{W_{eff}^2L_{eff}}$$

(3.11)

where  $V_T$  and  $\beta$  are the threshold voltage and current factor of the MOS transistor under test,  $W_{eff}$  and  $L_{eff}$  are the effective gate width and channel length of the MOSFET, and  $A_{1VT}$ ,  $A_{2VT}$ ,  $A_{3VT}$ ,  $A_{W^2}$ ,  $A_{L^2}$  and  $A_{\beta^2}$  are process related constants.

The variance in the drain current can then be derived as:

$$\frac{\sigma^2(\Delta I)}{I^2} = \frac{\sigma^2(\Delta \beta)}{\beta^2} + 4 \frac{\sigma^2(\Delta V_T)}{(V_P - V_S)^2}$$

(3.12)

where  $V_S$  is the Source voltage and  $V_P$  is the pinch off voltage.

For large enough transistors  $(L_{eff} > 1.2 \mu m)$  [BSR<sup>+</sup>95], the second and third term of Equations 3.10 and 3.11 can be neglected. The mismatches of the threshold voltage and current factor are then inversely proportional to the square root of the effective gate area  $(W_{eff}L_{eff})$ , which is the well-known Law of Area.

$$\sigma(\Delta V_T) = \frac{A_{VT0}}{\sqrt{W_{eff}L_{eff}}}$$

(3.13)

$$\frac{\sigma(\Delta\beta)}{\beta} = \frac{A_{\beta}}{\sqrt{W_{eff}L_{eff}}} \tag{3.14}$$

where  $A_{1VT}$  and  $A_{\beta^2}$  are restated as  $A_{VT0}$  and  $A_{\beta}$  respectively. Substituting these equations into (3.12), the mismatch of the drain current will also obey the Law of Area:

$$\frac{\sigma(\Delta I)}{I} = \frac{1}{\sqrt{W_{eff}L_{eff}}} \sqrt{A_{\beta}^2 + 4 \frac{A_{VT0}^2}{(V_P - V_S)^2}}$$

(3.15)

From the matching model given, the following conclusions can be drawn:

- When the gate length is larger than 1.2μm, the mismatches of the threshold voltage, current factor and drain current of MOSFETs are inversely proportional to the effective gate area (3.13 to 3.15).

This suggests that matching will become more and more critical as the technology is scaled down.

- The second and third terms of (3.10) and (3.11) account for the short and narrow channel effects respectively due to edge roughness [BSR+95]. The negative term in (3.10) indicates that the narrow channel effect makes a negative contribution to the mismatch of the threshold voltage. This is because, in contrast to the short channel effect which makes the depletion region controlled by the gate smaller (e.g. Drain-Induced-Barrier Lowering DIBL), the narrow channel effect increases it.

• The mismatch of the drain current depends on the overdrive voltage V<sub>P</sub> - V<sub>S</sub>. If the overdrive voltage is small (V<sub>GS</sub> < V<sub>T</sub> + 1.5V when the slope factor n ≈ 1), the mismatch in threshold voltage (second term in (3.15)) dominates and the mismatch of the drain current is roughly proportional to 1/√I<sub>D</sub> as A<sub>β</sub> can be neglected and I<sub>D</sub> ∝ (V<sub>P</sub> - V<sub>S</sub>)<sup>2</sup>. This value reaches a maximum and levels off in subthreshold region [LWMM98, FW94].

The matching properties of MOSFETs in the sub-threshold region have not been studied as extensively as that in the saturation region. However, as sub-threshold circuits have become more important in order to reduce power consumption, their matching properties have increased in importance. On the other hand, the matching properties of MOSFETs are simpler in the first order approximation because the mismatch is independent of the current level. The current equation of MOSFET in sub-threshold region in simple form (Equation 2.4) is restated here for convenience:

$$I_D = 2n\beta U_T^2 \exp \frac{V_P}{U_T} \left(\exp \frac{-V_S}{U_T} - \exp \frac{-V_D}{U_T}\right)$$

When  $V_D$  is large enough  $(V_D \gg \text{a few } kT)$ , such as when the drain is connected to the power rail, and  $V_S$  is connected to the ground, the equation can be simplified as:

$$I_D = 2n\beta U_T^2 \exp\frac{V_P}{U_T} = I_0 \exp\frac{V_G}{nU_T}$$

(3.16)

where  $I_0 = 2n\beta U_T^2 \exp{\frac{-V_T}{nU_T}}$ . By differentiating the above equation with respect to  $I_0$ , we have,

$$\delta I_D = \exp(\frac{V_G}{nU_T})\delta I_0$$

Rearranging the terms,

$$\frac{\delta I_D}{I_D} = \frac{\delta I_0}{I_0} \tag{3.17}$$

Therefore the mismatch of the drain current is independent of  $V_{GS}$ , which means that it is also independent of the current level. This explains why the mismatch of MOSFETs levels off in the subthreshold region [FW94].

Previous research has also shown that nMOSFETs have inherently better matching properties than pMOSFETs [LHC86]. This is because most of the CMOS fabrication processes are optimized for nMOSFETs. As a result, an extra ion implantation step is required to adjust the threshold voltage of pMOSFETs to a suitable value. Due to this additional threshold adjust implant, there is larger variation in the surface concentration in pMOSFETs. As as result, the matching of the threshold voltage in pMOSFETs is poorer than that in nMOSFETs. Furthermore, there is larger mobility variation due to the counterdoping in pMOSFETs.

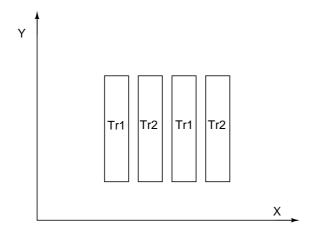

#### b. Reducing systemic mismatch

The topography and transistor matching relationship have been studied and it was shown that the common centroid and interdigitated waffle transistor layout structures (Figure 3.2) show almost no systematic mismatch. However, under die stress, the finger style transistor pair shows significant systematic mismatch [BGS96]. Moreover, dummy devices (or

Figure 3.2: Interdigitated finger layout of transistors Tr1 and Tr2.

etch guards) can be added to surround the array of devices to reduce the effect of variations in polysilicon etch rate. The dummy devices have the same spacing between the adjacent devices as that between the devices in the array. So, the boundary devices will not be over etched due to the larger spacing [Has01].

#### c. Modified MOS structures for reducing random mismatches

Suggestions for changing the structure or fabrication process of standard MOSFETs have also appeared in the literature, such as vertical MOSFETs [RKHS95] or the deposition and etch-back technique [HHG98]. These techniques were not studied or applied in this thesis because only a standard fabrication process was available.

#### 3.3.4 Matching Properties of BJTs and CLBTs

There have been few studies published on the matching properties of bipolar devices [TI96, TP98, Has01, CE96b], especially of CLBTs [Vit83, CHH96, PA89]. Most of the studies dealt with the vertical BJTs and they are summarized below.

Firstly, random fluctuations in base doping, emitter junction area, the densities of recombination center in the emitter base depletion region and Areato-Periphery ratio are significant sources accounting for the mismatches in BJTs [Has01]. Referring to Equation 2.1, they all play important roles in determining the collector current. The base doping and densities of recombination center are process dependent, which will affect the gains and cannot be controlled by circuit designers. Similar to MOSFETs, the larger the emitter area, the better will be the matching properties because effects of the random errors due to photolithography can be reduced. In vertical BJTs, minorities in base can also pass through the periphery of the base diffusion into the collector in addition to the vertical action (Figure 2.1), which will change the effective

resistance of the collector. Therefore, the Area-to-Periphery ratio should be maximized to reduce the side wall effects. The mismatch of the vertical BJTs due to the variations of emitter area can then be represented as [Has01]:

$$\sigma_{\delta_{I_C}} = \frac{1}{\sqrt{A_E}} \sqrt{k_a + \frac{k_r k_p}{\sqrt{A_E}}} \tag{3.18}$$

where  $A_E$  is the vertical emitter area,  $k_r$  is a constant, and  $k_a$  and  $k_p$  are constants representing the contributions of area and peripheral fluctuations respectively. The equation can then be simplified to be the Law of Area when the Area-to-Periphery ratio is large enough [TI96, TP98]:

$$\sigma_{\delta_{I_C}} = \sqrt{\frac{k_a}{A_E}} \tag{3.19}$$

Temperature gradient is another important source of mismatches in BJTs as mentioned in Section 3.3.2. Since the temperature coefficient of the base-emitter voltage is about  $-2mV/^{\circ}C$ , that of the collector current then will be equivalent to  $80,000ppm/^{\circ}C$  [Has01]. Therefore, the location of the BJTs differential pairs should be carefully planned and placed far away from any power transistors. Temperature gradient will be a big problem for matching if the power consumption of the chip is high.

For the CLBTs, the above results are still applicable. In addition, there are some important published results that motivated the systematic and quantitative study of matching properties of CLBT in this thesis.

1. It has been shown that gated lateral bipolar action in weakly inverted MOS transistors can improve the matching properties. This shines a light that the matching properties of CLBT would be better than that of MOS [CHH96]. This is because, under the same bias conditions, CLBTs matching mainly depends on geometrical and processing factors (lateral and vertical emitter areas and doping concentration of the base) that are different from and better controlled than those of MOSFETs (length and width of the channel, surface doping and oxide properties) [Arr89].

- 2. The CLBTs have been used to implement highly accurate circuits such as a Gilbert gain cell (a two-quadrant analog multiplier) [PA89] and current sources in a silicon cochlea [vSFV96]. Both circuits have demonstrated that CLBTs have better matching properties than MOSFETs.

- 3. The Law of Area can be applied in bipolar devices where WL is the effective lateral emitter area [TP98].

There have been several studies comparing the matching properties of CLBTs and MOSFETs. In these studies, CLBTs are generally thought and shown to have better matching properties than MOSFETs in these processes and were even used for replacing MOSFETs in some critical matching circuits. However, most of the studies did not make fair enough comparisons between the CLBTs and MOSFETs. They are summarized in Table 3.1.

| Pape   | er  | Comparisons    | $\operatorname{Process}$ | CLBT           | MOS-                 | Area                   |

|--------|-----|----------------|--------------------------|----------------|----------------------|------------------------|

|        |     |                |                          |                | $\operatorname{FET}$ | $\operatorname{ratio}$ |

| [Vit83 | 3]  | Current Mirror | <i>p</i> -well           | npn            | <i>n</i> -type       | CasM                   |

| [PA89  | 9]  | Current Mirror | $3\mu m p$ -well         | npn            | $n	ext{-type}$       | CasM                   |

| [CHC9  | 96] | Current Mirror | $0.8 \mu m$              | NMOS with      | n-type               | 1:1                    |

|        |     |                | twin-well                | BJT action     |                      |                        |

| [vSFV  | 96] | Current Mirror |                          | $npn(1.5\mu m$ | $n$ -type $(2\mu m$  |                        |

|        |     |                |                          | p-well)        | n-well)              |                        |

| [RHL9  | 97] | Photoreceptor  | $2\mu m \ n$ -well       | pnp            | <i>p</i> -type       | 2:1                    |

Table 3.1: Previous results comparing the matching properties of MOSFETs and CLBTs.

The first four publications compared the mismatch of current mirrors and the last one compared the signal-to-offset of a photoreceptor. CasM means that the CLBTs were operated directly as MOSFETs for comparison, which means the gate area is at least 10 times smaller than a normal MOSFET with similar layout area as the CLBT. Therefore, the CLBTs were compared with MOSFETs which had effectively smaller layout areas. It should also

be noted that in [vSFV96], different fabrication processes were used. The CLBT design was fabricated using ECPD15 (a single-poly double-metal  $1.5\mu m$  CMOS process) at ES2 (Grenoble, France) [vSFV96] while the MOSFET design used a standard double-poly double-metal  $2\mu m$  CMOS technology at MOSIS [WKLM92]. Moreover, the publications also compared poorer matching MOSFET type in the corresponding process (e.g. nMOSFETs in a p-well process and pMOSFETs in an n-well process) with CLBTs. However, as mentioned in Section 2.3, due to counter doping, the matching properties of the MOSFETs formed in the well is poorer (pMOSFETs are poorer than pMOSFETs in an p-well process and pMOSFETs are poorer than pMOSFETs in a p-well process) [LHC86]. This motivates the comparison between the matching properties of CLBTs with the better matching MOSFET (nMOSFET in p-well process).

# 3.4 Summary

This chapter has summarized previous research results on the matching properties of CMOS and bipolar devices. Special emphasis was placed on CMOS and the importance of, equations for and factors affecting the mismatches in these devices. It was also pointed out that fairer comparison between MOSFETs and CLBTs are needed because previous research mainly compared the mismatch of MOSFETs of much smaller area than that occupied by the CLBTs.

# Chapter 4

# CMOS Compatible Lateral Bipolar Transistors (CLBTs)

# 4.1 Introduction

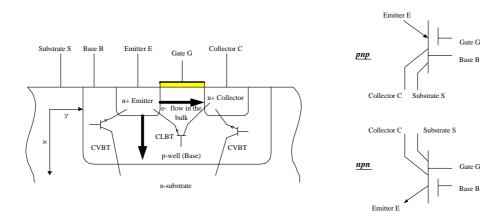

Compatible Lateral Bipolar Transistors (CLBTs) and Compatible Vertical Bipolar Transistors (CVBTs) are both parasitic bipolar devices found in a CMOS process (Figure 4.1). Since CVBTs can only be used in common-collector configurations, they are of limited use to circuit designers and will not be discussed in detail in this thesis.

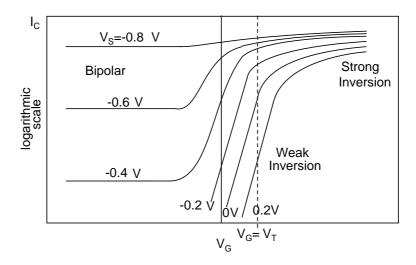

In this chapter, the structure and operation of CLBTs are first introduced. Then the DC model proposed by Arreguit [Arr89] is presented. CLBTs are modeled as BJTs with some special characteristics including low current gain and low Early voltage. Moreover, the collector current actually depends on the gate voltage, which is called the residual gate effect. These characteristics are all discussed in detail. Following this, applications of CLBTs in the literature and the design and layout of CLBTs for practical use are presented. Finally, the gains of CLBTs, current-voltage (I - V) characteristics of pnp CLBTs, nMOSFETs, and CLBTs operating as pMOSFETs fabricated using the AMI-ABN 1.5 $\mu m$  n-well process, and their measurement setup are given.

# 4.2 Structure and Operation